本文由面包板社区博主“小马哥”原创,未经允许不得转载!

面包板社区博客大赛正在进行中,了解详情请撮→2017面包板社区博客大赛!第一季开赛!

博客大赛奖项设置:

特等奖(1名):3000元 + 奖杯

一等奖(2名):1500元 + 奖杯

二等奖(3名):800元 + 奖杯

三等奖(5名):500元

博客链接:https://www.mianbaoban.cn/blog,手动输入网址前往开博参赛!

今天我们通过两个静态数码管实现0-99的计数,且每500ms计一个数。

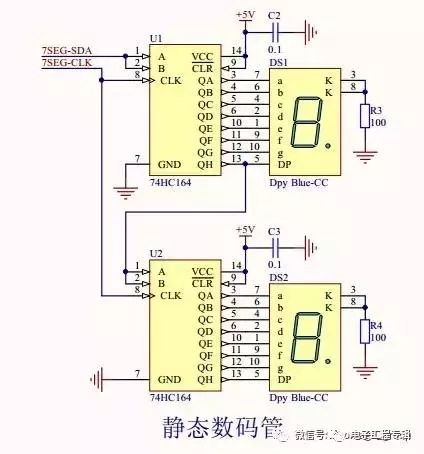

我们首先来看看基于74HC164的静态数码管显示的电路原理图~

这就是两个静态数码管的原理图。大家从图中可以看出,两个数码管的公共端3,8引脚全部接的是GND,所以说这是两个共阴数码管;从图中还可以看出这两个数码管由两个74HC164芯片驱动,并且第二个74HC164芯片的AB引脚接的是第一个芯片的QH。那么下面我们通过数据手册来看看这两个芯片是如何驱动两个共阴数码管的,并且在硬件电路中为什么这么接呢?

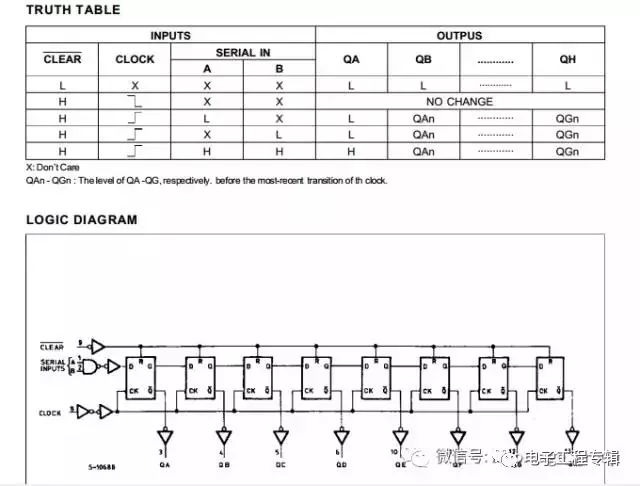

这是在数据手册中找到的真值表和逻辑结构图。

下面我就带着大家一起看看这个真值表和逻辑结构框图。

首先从真值表中可以看出,无论clock及AB引脚为什么电平,只要clear为低电平,则QA,QB,...,QH的输出均为低电平,我们从硬件电路图中可以看出,在电路图中clear引脚已连接至VCC,所以对于clear为低电平的情况就不用考虑;其次在clock的下降沿,无论AB输入什么电平,QA,QB,...,QH的输出均不改变;再者,在clock的上升沿,只要AB输入有一个为低电平,QA的输出为低电平,且QB的输出为QA的上一个状态,QC的输出为QB的上一个状态....;最后,在clock的上升沿,AB同时输入为高电平时,QA的输出为高电平,且QB的输出为QA的上一个状态,QC的输出为QB的上一个状态....。

大家从上面的描述中可以发现,在时钟的上升沿,QA的输出值为AB相与之后的结果,而QB的输出值为QA的上一个状态,QC的输出值为QB的上一个状态,依次下去...。这是为什么呢?从逻辑结构框图中可以看出,这是一个8位的移位寄存器,所谓移位寄存器的工作原理,类似于实际中东西的传递,如果依次来8个时钟的上升沿呢,这个时候最开始AB相与的结果传到QH上,第二次AB相与的结果传到QG上,一直到第八个AB相与的结果才到QA上,这就是移位寄存器的工作过程。原理图中第二个芯片的AB输入接在第一个芯片的QH输出,其实就是将8个串联的D触发器合并成16个D触发器的串联,这个时候需要16个时钟的上升沿,第一次的输出才会传到第二个芯片的QH上,依次传递...。

明白了原理之后,下面我们开始FPGA程序的编写,让这两个数码管实现0-99的计数,计到99之后回0继续计数。

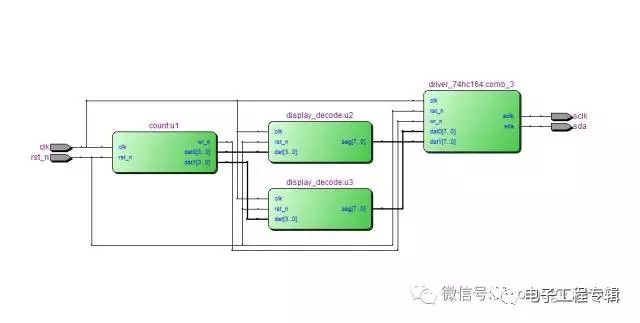

这就是FPGA综合编译之后的硬件结构框图,由计数模块“count”,数码管编码模块“display_decode”及74HC164的驱动模块“driver_74hc164”这三部分组成。其中计数模块实现0-99的计数,编码模块实现0-9数字对应到数码管显示的编码值,驱动模块则实现74HC164移位寄存器的功能。各部分代码太长,下面把顶层文件的元器件例化代码贴出来供参考。

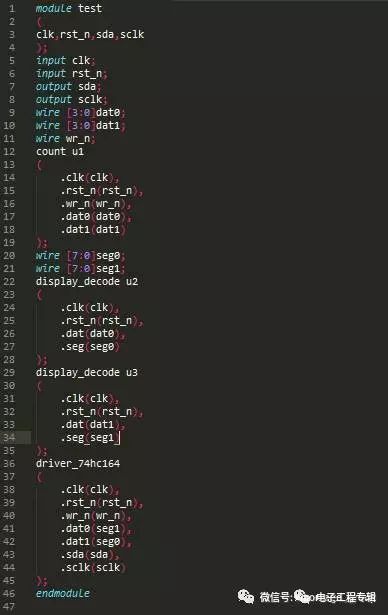

这就是Verilog语言顶层元器件例化的代码格式。

我们将编写后的代码下载到FPGA板子中,看看实际的效果怎么样。这里因为0-99计数是每500ms计一次数,如果用Modelsim进行仿真的话,估计得等一个世纪才能仿真结束,到时候电脑非得卡死不可,所以这里就不仿真了。

最后实际的效果和我们之前预想的完全一样哦,说明设计通过了,哈哈哈哈~~~~

看完本文有收获?请分享给更多人

关注「电子工程专辑」,做优秀工程师!

回复关键词有干货:电路设计丨电容丨三极管丨PCB丨接地‧‧‧‧‧‧

长按二维码识别关注

阅读原文可一键关注+历史信息