来源:内容来自微信公众号观芯志

,作者知乎用户forever snow,

谢谢。

这是一个比较有意思的问题。乍一看貌似很有道理的样子,通过增大芯片面积,一个芯片中可以放下更多的晶体管,更多的晶体管可以实现功能更复杂,性能更高的芯片呢。为什么半导体行业却没有这么发展呢?

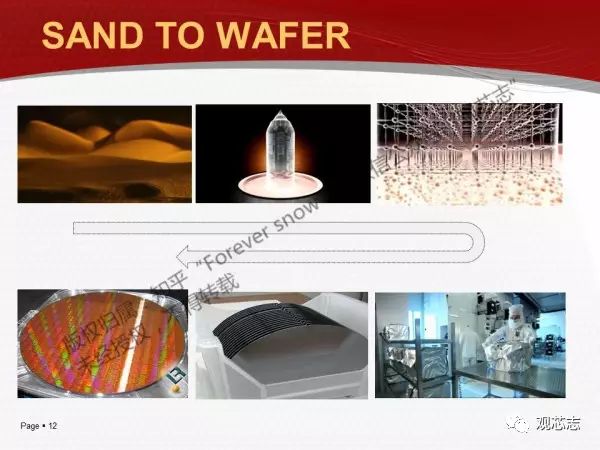

首先我们看一下,一颗芯片是怎样制造出来的呢?在半导体制造中,先将单晶硅棒经过抛光、切片之后,成为了晶元(wafer)。而每一片wafer经过掺杂、光刻、等步奏后形成一个个芯片。

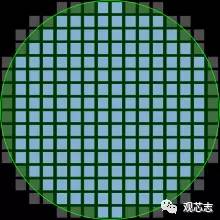

成品的wafer一般长成下图,wafer内一小块一小块的正方形我们称之为die,即未封装的芯片。

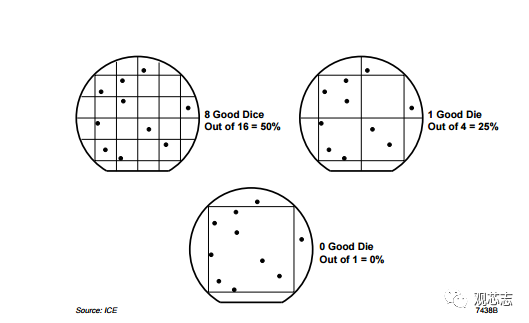

那么如果晶元的尺寸不变而增大单个芯片的大小会有什么后果呢?1)一片wafer中芯片个数变少 这一点很好理解,比如下图,圆形是wafer的范围,正方形为一个die。随着芯片面积的增大,相同大小一片wafer中包好的芯片个数从16变成4再到1。这样就会造成制造成本很高。 2)良率变差 良率可以简单理解为,一片wafer中可以正常工作的芯片。在芯片制造中由于灰尘或者切割或工艺等问题,会使同一片wafer中若干区域损坏,造成芯片报废。我们还是一下图为例。黑色点为损坏点。单个芯片面积越大良率越低。

那如我们同时将晶元的面积变大,这样是不是就可以解决以上两个问题了? 下图为晶元面积的发展史,很可惜晶元面积的增长速度较慢。如果不进行晶体管尺寸缩小,仅仅依靠晶元变大,那么半导体发展将远远的落后于摩尔定律。

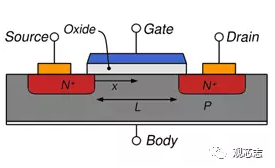

选用更先进的工艺除了成本和良率的好处之外还有哪些方面的优势呢?一个MOS管的基本结构如下:

每一代新工艺节点,晶体管的沟道长度L变小。沟道长度变小后,晶体管有更快的反应速度,更低的控制电压。

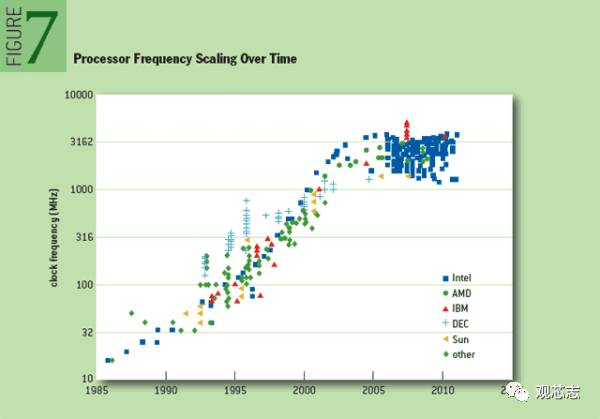

1)更快的频率 随着工艺节点的不断缩小,芯片的频率越来越高。

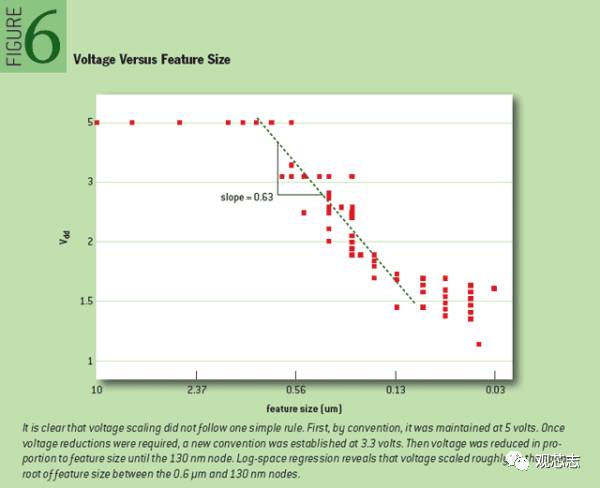

2)更低的电压 而芯片的功耗是与电压成平方关系,电压的降低,可以极大的减少功耗。

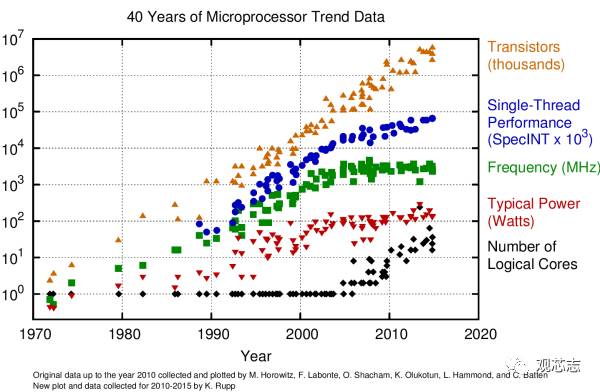

由上可知,芯片的性能(频率、面积、功耗)与芯片中集体管个数并没有必然联系,而仅仅通过增大面积无法达到提高性能的目的。 下图是近40年来芯片发展图,由图可知通过不断缩减晶体管尺寸,确保了近40年来半导体业高速的发展。

延伸阅读

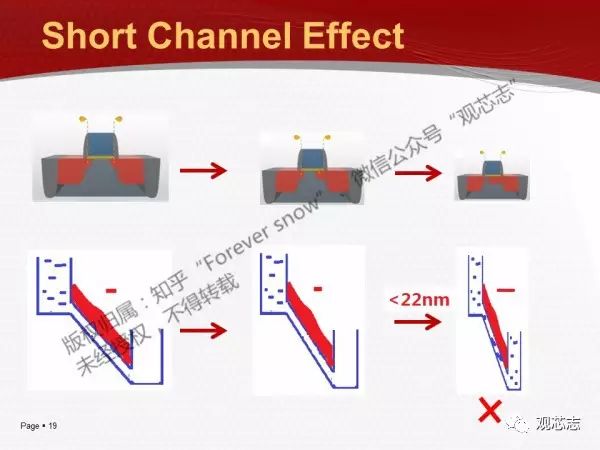

但是进入28nm以后再按照以往的经验来缩减晶体管尺寸,将会失效。短沟道效应造成晶体管无法关断。目前业内通过Fin-FET, SOI等技术来解决这个问题。

今天是《半导体行业观察》为您分享的第1312期内容,欢迎关注。

关注微信公众号

半导体行业观察

,后台回复关键词获取更多内容

回复

科普

,看《第三代半导体科普,国产任重道远》

回复

争霸

,看《晶圆代工争霸战四部曲(了解各晶圆厂的前世今生,非常详细!建议收藏!) 》

回复

指南

,看《半导体专业留学海外指南(1): 专业方向选择》

回复

财报

,看《18家半导体企业财报汇总,几家欢喜几家愁》

回复

国产手机

,看《谨以此文献给国产手机背后的劳动者》

回复

指纹

,看《面板厂将指纹识别芯片革命到底 》

回复

OLED

,看《一文看懂我国OLED全产业链,除了京东方还有啥值得骄傲的?》

回复

缺货

,看《半导体行业缺货危机重现 这10大领域面临洗牌?》

想成为“半导体行业观察”的一员?回复“

投稿

”,了解我们的福利与待遇吧~

想了解半导体人都去参加哪些展会?回复

“展会”/“展览”/“研讨会”/“论坛”

,看《2017最新半导体展会会议日历》

【关于转载】:转载仅限全文转载并完整保留文章标题及内容,不得删改、添加内容绕开原创保护,且文章开头必须注明:转自“半导体行业观察icbank”微信公众号。谢谢合作!

【关于征稿】:欢迎半导体精英投稿(包括翻译、整理),一经录用将署名刊登,红包重谢!签约成为专栏专家更有千元稿费!来稿邮件请在标题标明“投稿”,并在稿件中注明姓名、电话、单位和职务。欢迎添加我的个人微信号 MooreRen001或发邮件到 [email protected]

点击阅读原文加入摩尔精英