为了方便各位同学交流学习,解决讨论问题,我们建立了一些微信群,作为互助交流的平台。

2.告知:姓名-课题组-研究方向,由编辑审核后邀请至对应交流群(生长,物性,器件);

欢迎投稿欢迎课题组投递中文宣传稿,免费宣传成果,发布招聘广告,具体联系人:13162018291(微信同号)

【研究背景】

近年来,二维层状材料(2DLMs),如过渡金属二硫化物(TMDs),展现出了卓越的电子特性,包括原子级薄的结构、厚度依赖的带隙(E

g

)、无表面悬挂键,以及静电调制能力等。其中MoS

2

由于其优异的电学性能,作为高性能场效应晶体管(FETs)的半导体沟道材料引起了广泛关注。受益于先进的异质结技术和成熟的大规模转移方法,二维/三维混合维度异质结需要晶格失配和逐层耦合界面。二维/三维混合维度异质结广泛应用于隧穿晶体管、光电二极管和场效应晶体管中。此外,由于三维半导体中载流子迁移率和有效质量呈负相关,使用较小的有效质量可以实现高载流子迁移率。同时,通过掺杂沟道的内部多数载流子输运机制可获得n型或p型转移特性。

随着硅的潜力逐渐被充分利用,摩尔定律正接近其物理极限。在后摩尔时代,实现更高的晶体管密度、更快的速度,并减少漏电流(I

leak

)以降低静态功耗(P),同时确保逻辑准确性变得越来越具有挑战性。此外,P的缩放需要低亚阈值摆幅(SS);然而,在传统FET中,热发射的固有SS在300 K时保持在60 mV dec

−1

以上。随着尺寸继续缩小,晶体管的性能逐渐降低,需要低SS来可靠地实现集成电路的功能并满足低P的需求。因此,在不损害器件性能的情况下降低驱动电压的最简单有效的方法是转向具有超陡峭开关行为的器件结构—即SS应很小。

近期已有研究提出了超越CMOS技术的2D范德瓦尔斯异质结电子器件技术,包括隧穿FET和铁电FET。其中,基于2D/3D混合维度异质结的结型场效应晶体管(JFETs)正在兴起。JFETs的工作模式并不完全依赖于介电层,从而避免了电荷陷阱。此外,根据之前关于使用简便转移方法的2D/3D混合维度异质结的报道,发现它们可以在异质结区域形成有效的耗尽区。在混合维度JFET中,隧穿效应是一个关键因素,使电子能够从一个半导体区域穿过势垒到另一个区域。这使得突破传统金属

-

氧化物

-

半导体FET的60 mV dec

−1

的SS限制成为可能。

然而,大多数先前的研究集中在通过底栅调制的2D/Si和2D/Ge异质结基JFETs上,缺乏对混合维度JFETs中栅极漏电(I

leak

)和结温的研究。值得注意的是,宽带隙材料(如GaN,E

g

= 3.4 eV)具备的优势,如可控的掺杂浓度、高击穿电场、大的工作电压窗口和成熟的外延生长技术,尚未在通过底栅调制的2D/3D JFETs中得到充分利用。值得注意的是,在外延层适当的掺杂浓度下,它们有望通过2D材料的厚度工程作为调制TMDs沟道的有前景的栅端。TMDs/GaN混合维度异质结已被研究用于UV-vis光电二极管。迄今为止,MoS

2

/GaN的顶栅调节效果令人满意。然而,还没有关于直接使用底部GaN薄膜调节2D TMDs沟道中载流子浓度分布的报道。目前,大多数JFETs都处于耗尽模式(D模式),这通常会导致在没有栅极电压的情况下功耗较高。因此,有必要通过厚度工程实现低功耗的增强模式(E模式),并通过外部电场可逆地改变其工作模式。

【成果介绍】

鉴于此,华南师范大学的高伟研究员,孙一鸣副研究员团队和广东省工业分析检测中心陈文龙高级工程师合作发表了题为“MoS

2

/GaN Junction Field-Effect Transistors with Ultralow Subthreshold Swing and High On/Off Ratio via Thickness Engineering for Logic Inverters”的工作在Advanced Functional Materials期刊上。该研究在2D沟道的厚度工程下,首次使用缓冲氧化物刻蚀(BOE)和干转移方法构建了同型MoS

2

/GaN JFET。与传统的基于Si的FET相比,MoS

2

/GaN JFET没有栅极氧化物层,这简化了工艺并实现了E模式。截面透射电子显微镜(TEM)和拉曼光谱结果表明,异质结界面清洁平整,具有显著的层间耦合效应。通过光致发光(PL)光谱和理论计算验证了耗尽区中的I型能带排列。当MoS

2

厚度为10 nm时,在二极管模式下,器件整流比达10

6

,在过渡电压(V

trans

)为5 V时,正向电流由直接隧穿(DT)或Fowler

–

Nordheim隧穿(FNT)主导。在室温JFET模式下,JFET为E模式。当V

ds

= 0.1 V时,器件表现出超低的SS(60.9 mV dec

−1,玻尔兹曼极限为60 mV dec

−1

)和高I

on

/I

off

比(10

6

)。饱和电流密度(J

ds

)在V

ds

= 1.5 V时达到最大值0.16 µA µm

−1

,而异质结外的界面态密度低至3.9 × 10

10

cm

−2

。随着MoS

2

厚度从6 nm增加到16 nm,工作模式从E模式转变为D模式。当MoS

2

厚度分别为6、10和16 nm时,计算得到MoS

2

侧的耗尽宽度为5.75、5.52和4.81 nm。通过计算机辅助设计(TCAD)模拟成功显示了两种不同厚度的MoS

2

沟道中电子浓度分布的示意图。最后,制造了N型负载逻辑逆变器,当MoS

2

厚度为6 nm时,在V

ds

= 0.5 V时最大电压增益达4,最小静态P为25 nW。当MoS

2

厚度为12 nm时,在V

ds

= 0.5 V时实现了1 nW的最小静态P。该研究中的JFET的性能,包括SS和I

on

/I

off

比,优于大多数其他2D/2D和2D/3D JFETs。这些结果为实现新一代基于TMD/GaN混合维度异质结的逻辑电路电子器件提供了参考。

【图文导读】

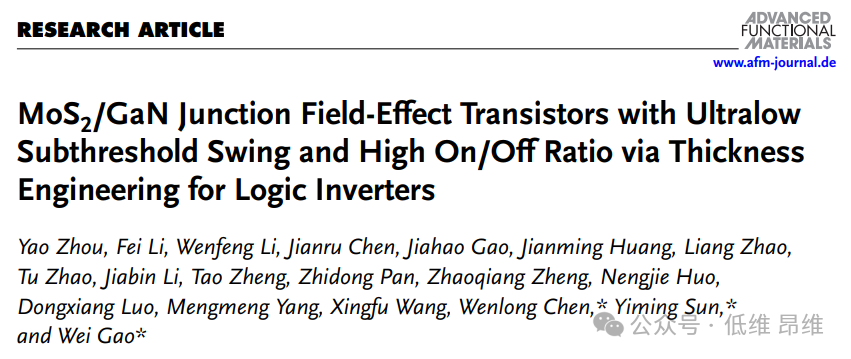

图 1. 器件结构和表征 a) MoS

2

/GaN JFET的示意图。 b) MoS

2

/GaN JFET的SEM图像。 c) AFM图像及沿虚线的相应高度剖面。 d) 异质结的高分辨率截面TEM图像。 e) 异质结的EDX元素映射图像。 f) MoS

2

、GaN和MoS

2

/GaN异质结的拉曼光谱。

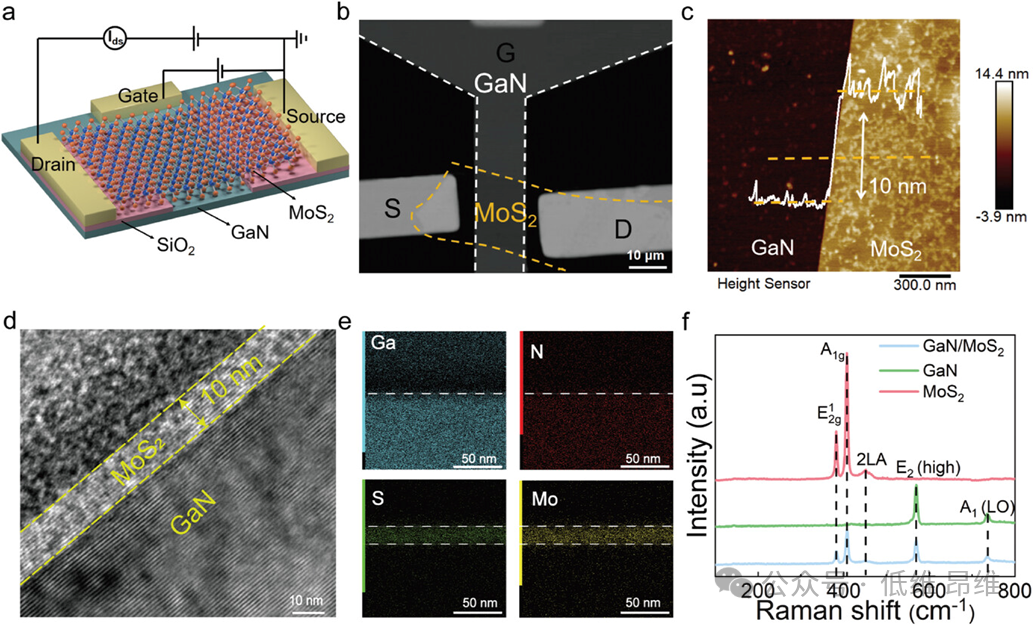

图 2. 二极管模式下的I

ds

–V

ds

曲线和传输机制。 a) MoS

2

/GaN异质结的线性I

gd

–V

gd

曲线。 b) MoS

2

/GaN异质结器件正向电流的Fowler–Nordheim图拟合。 c) MoS

2

和GaN接触处的能带图。 d) V

gd

< 0 V时I型MoS

2

/GaN异质结构的能带图。 e) 0 V < V

gd

< 5 V时的能带图。 f) 5 V < V

gd

< 10 V时的能带图。

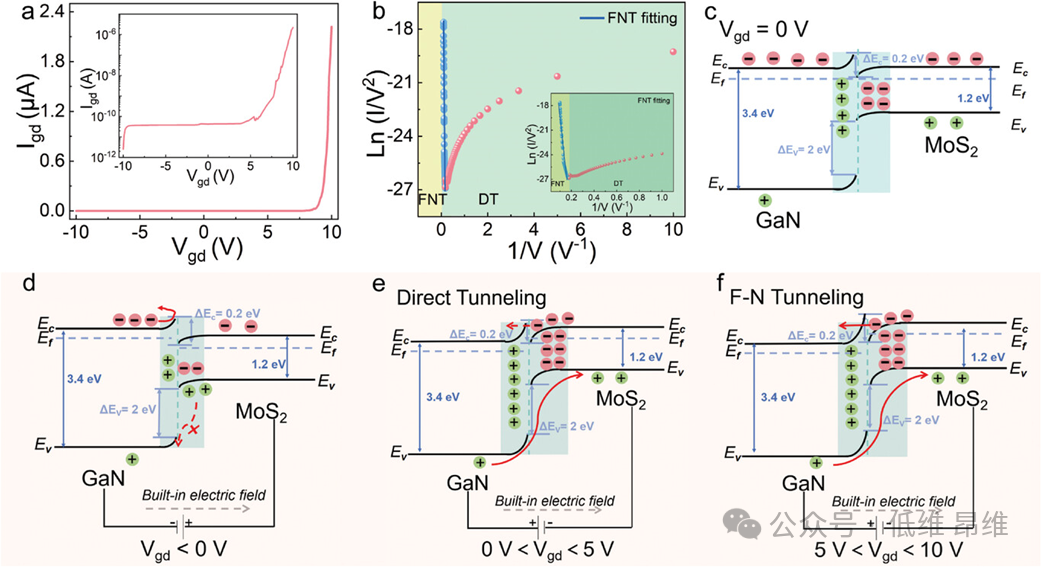

图 3. JFET模式下的电学性能 a) 不同V

ds

下E-JFET的室温对数转移特性。 b) 不同V

ds

下E-JFET的室温线性转移特性。 c) E-JFET的输出特性。 d) E-JFET的I

on

/I

off

比和SS随V

ds

的变化。 e) 不同温度下的D模式转移曲线。 f) D-JFET的肖特基势垒高度随V

g

的变化。

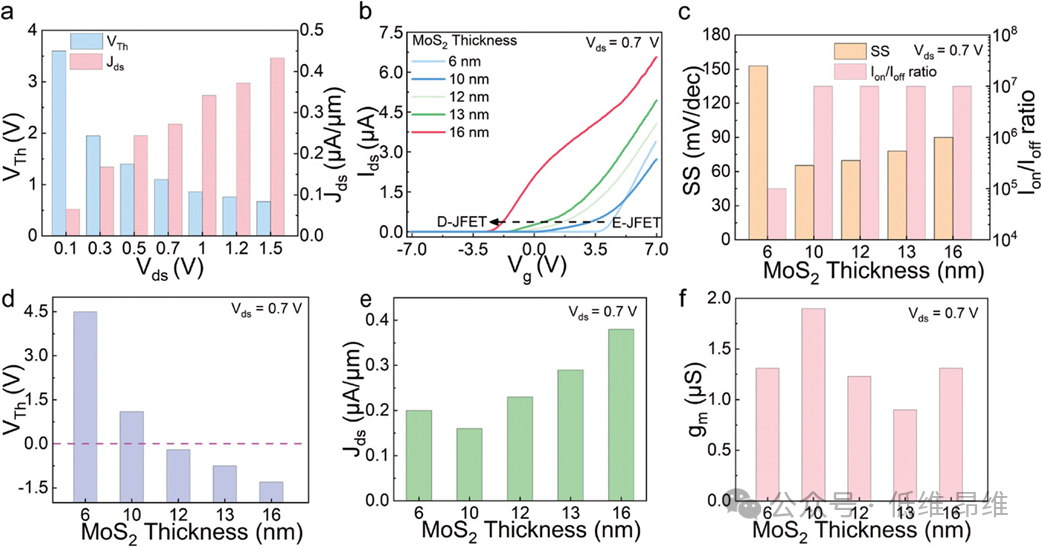

图 4. 不同V

ds

和MoS

2

厚度下MoS

2

/GaN JFET的电学性能 a) JFET的V

Th

和J

ds

随V

ds

的变化。 b) 不同厚度JFET在V

ds

= 0.7 V时的转移曲线。 c) JFET的SS和I

on

/I

off

比在V

ds

= 0.7 V时随MoS

2

厚度的变化。 d) JFET的V

Th

在V

ds

= 0.7 V时随MoS

2

厚度的变化。 e) JFET的J

ds

随MoS

2

厚度的变化。 f) JFET的g

m

在V

ds

= 0.7 V时随MoS

2

厚度的变化。

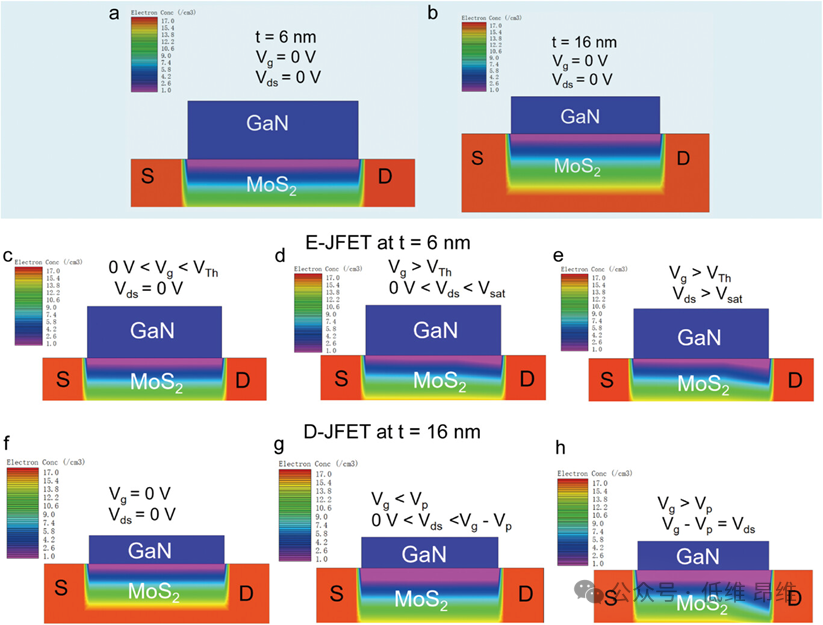

图 5. MoS

2

厚度为6和18 nm时MoS

2

/GaN JFET的TCAD模拟示意图 a, b) 当t = 6 nm和t = 16 nm时耗尽区的放大图。 c–e) 不同V

g

和V

ds

下E-JFET的耗尽区状态。 f–h) 不同V

g

和V

ds

下D-JFET的耗尽区状态。

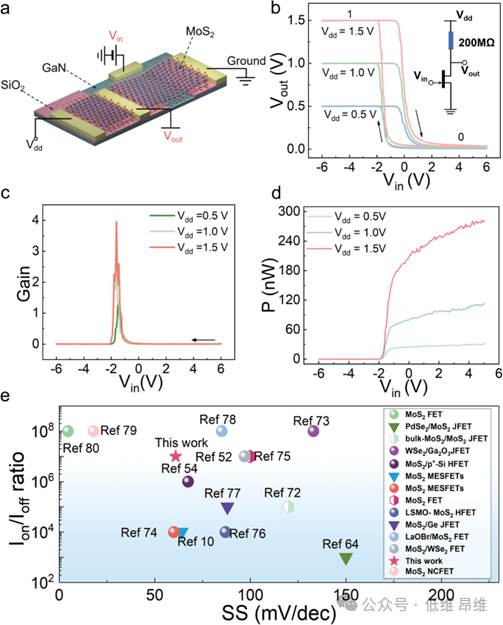

图 6. a) 逆变器的示意图。 b) 逆变器的V

out

-V

in

特性。 c) 不同V

dd

水平下的增益。 d) 不同V

dd

下的功率P。 e) 与其他MoS

2

FET的I

on

/I

off

比和SS的比较图表。

【总结展望】

总之,本工作设计了一种由n型MoS

2

和n型GaN薄膜组成的混合维度JFET,这两种材料形成I型能带排列,用于制造陡峭斜率晶体管。得益于平整紧凑的界面、强耦合效应和良好的整流特性,当MoS

2

厚度为10 nm时,该JFET在V

ds

= 0.1 V下展现出极低的亚阈值摆幅(SS)60.9 mV dec

−1

,高开关比(I

on

/I

off

)10

6

,以及超低的泄漏电流(I

leak