本文介绍了基于二维材料的新型晶体管,使用六角氮化硼(h-BN)作为介电质和金属电极。研究解决了通过化学气相沉积(CVD)生长的h-BN的漏电流和过早介电击穿问题,具有高内聚能的金属电极的应用被强调。成果在Nature Electronics上发表,展示了金属电极对降低漏电流和提高介电强度的重要作用。

最早的商用晶体管采用了全硅的自上向下结构,但随着晶体管尺寸的缩小,漏电流和介电质击穿问题出现。英特尔用二氧化铪(HfO2)替代SiO2,二维(2D)半导体材料如二硫化钼(MoS2)和二硒化钨(WSe2)被提议作为未来商用晶体管的替代候选材料。然而,它们与大多数介电材料之间的界面存在问题。

阿卜杜拉国王科技大学Mario Lanza团队在Nature Electronics上发表了关于使用六角氮化硼(h-BN)作为介电质和金属电极的二维材料晶体管的研究。该研究展示了具有高内聚能的金属栅极电极如何减轻通过CVD生长的多层h-BN的漏电流和过早介电击穿。

使用Pt和W等高内聚能金属电极,相比Au电极,可以降低约500倍的栅极漏电流,并提供约5倍高的介电强度。这一表现通过多个器件和统计方法得到验证,包括基于CMOS技术的微芯片。

该研究为加速二维材料在固态微电子器件和电路中的应用提供了可能。高质量h-BN单晶等耗材,器件和光刻掩膜版定制等微纳加工服务,以及各种测试分析也得到了简要介绍。

为了方便各位同学交流学习,解决讨论问题,我们建立了一些微信群,作为互助交流的平台。

2.告知:姓名-课题组-研究方向,由编辑审核后邀请至对应交流群(生长,物性,器件);

欢迎投稿欢迎课题组投递中文宣传稿,免费宣传成果,发布招聘广告,具体联系人:13162018291(微信同号)

【研究背景】

【研究背景】

最早的商用晶体管采用了全硅的自上向下结构:具体来说,包括多晶硅栅极电极、薄层(约20 nm)SiO

2

介电质和硅体沟道。到21世纪初,晶体管的尺寸已经缩小到了一个程度,使得通过SiO

2

(此时厚度仅约2 nm)的漏电流在0.6 V电压下可能超过10 A/cm

2

,这会导致功耗增加和介电质过早击穿(即器件失效)。2004年,英特尔提出了一个解决方案,用二氧化铪(HfO

2

)替代SiO

2

。HfO

2

具有更高的介电常数(

k

),可以使用更厚的层(这减少了漏电流并延缓了介电击穿)产生形成沟道所必需的相同的电容效应。英特尔于2008年开始商业化这项技术,现在所有缩小尺寸的晶体管都基于高

k

/金属栅极技术。

二维(2D)半导体材料—如二硫化钼(MoS

2

)和二硒化钨(WSe

2

)—被提议作为未来商用晶体管中替代Si的候选材料。这些材料的厚度薄且精确(几埃米),可以对沟道提供出色的静电控制,这应该会使得朝向衬底的电流可忽略、声子散射非常低以及短沟道效应减弱。然而,2D半导体与大多数介电材料—包括氧化铪(HfO

2

)、氧化铝(Al

2

O

3

)和氧化钽(Ta

2

O

5

)—之间的界面存在问题。特别是2D材料表面缺少悬挂键阻碍了共形涂层,并在界面处产生多个原子缺陷。在器件层面这是灾难性的,因为它会增加晶体管的栅极漏电流、滞后效应、亚阈值摆幅和阈值电压不稳定性。

解决这个问题的一个方案是使用二维六方氮化硼(h-BN)作为栅极介电质,因为它形成无缺陷的范德华界面,从而带来性能提升,如更高的沟道迁移率。此外,h-BN可以提供低漏电流(1.3 nm厚的堆叠在0.6 V电压下低于10 A/cm

2

)和高介电强度(约21 MV/cm)。然而,到目前为止,这只在使用机械剥离的二维材料时有效。当使用化学气相沉积(CVD)合成的二维材料时,由于h-BN中存在本征缺陷(原子空位、应变键、杂质和嵌入在二维层状h-BN中的几个原子宽的非晶区域),会降低器件性能。目前已经探索了各种缓解这个问题的策略,包括使用单层分子晶体(如10-苝-四羧酸二酐)作为种子层,使用可氧化形成高

k

介电质的二维半导体(如Bi

2

O

2

Se氧化成Bi

2

SeO

5

),以及使用离子晶体(如CaF

2

)作为栅极介电质。然而,这些方法面临集成挑战,到目前为止工业界还没有很好地采用。

【成果介绍】

鉴于此,阿卜杜拉国王科技大学的Mario Lanza团队发表了题为“Two-dimensional-materials-based transistors using hexagonal boron nitride dielectrics and metal gate electrodes with high cohesive energy”的工作在Nature Electronics上。这篇工作展示了具有高内聚能的金属栅极电极可以用来减轻通过CVD生长的多层h-BN的漏电流和过早介电击穿。与金属氧化物(如HfO

2

)不同,后者的击穿可能在低电场下由移动的氧离子触发,而h-BN不含导电原子,因此金属渗透是触发击穿的必要条件。结果表明,使用具有高内聚能的金属电极—Pt和W可以提供相比于使用Au电极约500倍低的栅极漏电流和约5倍高的介电强度。本工作通过23个样品中的867个器件统计地说明了这种表现,其中包括基于180 nm节点互补金属—氧化物—半导体(CMOS)技术的微芯片。

【图文导读】

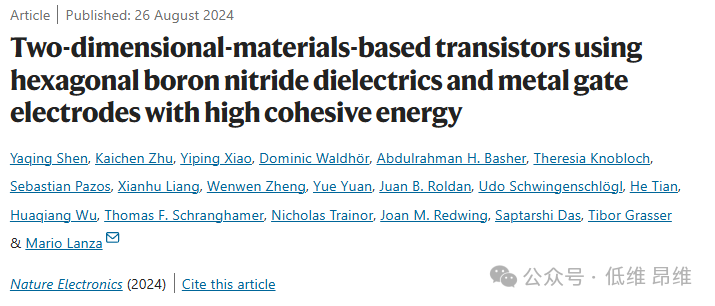

图1:Pt/h-BN/Pt和Au/h-BN/Au器件中的介电击穿和漏电流。a, 4

×

4交叉阵列Pt/多层h-BN/Pt(器件尺寸4

×

4 µm

2

)的扫描电子显微镜(SEM)图像。比例尺为10 µm。b, 在Au/多层h-BN/Au器件中测得的形成I-V曲线。c, 在Pt/多层h-BN/Pt器件中测得的I-V曲线。d, 介电强度(E

b

)与介电常数(

ε

r

)的关系图。e, Au/多层h-BN/Au和Pt/多层h-BN/Pt器件中测得的电流密度与电压特性。f, Au/多层h-BN/Au和Pt/多层h-BN/Pt器件的电流密度箱线分布图。g, 4

×

4交叉阵列Au/多层h-BN/Pt器件(器件尺寸4 × 4 µm

2

)的光学显微镜图像。h, 以Au为阳极的Au/多层h-BN/Pt器件中测得的形成I-V曲线。i, 以Pt为阳极的Au/多层h-BN/Pt器件中显示低漏电流的不同器件的I-V图。

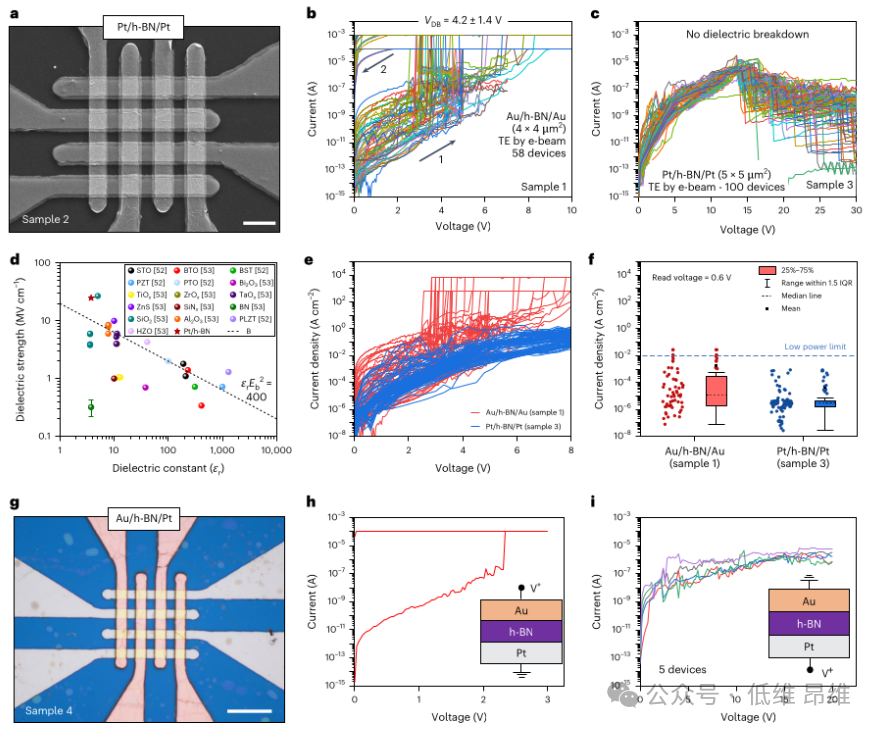

图2:Pt/h-BN/Pt和Au/h-BN/Au器件的新制和施加偏压后的形态和化学特征分析。a, b, 新制Pt/h-BN/Pt器件(a)和受压Pt/h-BN/Pt器件(b)的横截面透射电子显微镜(TEM)图像。c, 受压Pt/h-BN/Pt器件的B、N和Pt信号的能量色散X射线(EDX)图谱。d, e, 新制Au/h-BN/Au器件(d)和受压Au/h-BN/Au器件(e)的横截面TEM图像。f, 在发生严重金属渗透的位置(虚线圆圈内)的受压Au/h-BN/Au器件的B、N和Au信号的电子能量损失谱(EELS)图谱。

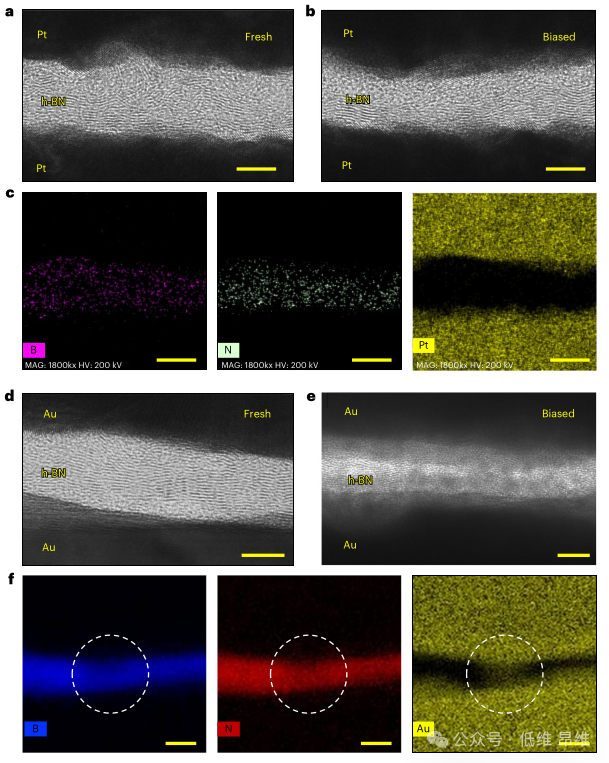

图3:小尺寸Pt/h-BN/Pt和Au/h-BN/Au器件中的介电击穿和漏电流。a, 交叉点Pt/h-BN/Pt器件(器件尺寸370

×

250 nm²)的扫描电子显微镜(SEM)图像。b, 在横向尺寸为320

×

420 nm²的Au/多层h-BN/Au器件中测得的电流与电压特性。c, 在横向尺寸为500

×

500 nm²的Pt/多层h-BN/Pt器件中测得的电流与电压特性。d, Au/多层h-BN/Au和Pt/多层h-BN/Pt器件中测得的电流密度与电压特性。e, Au/多层h-BN/Au和Pt/多层h-BN/Pt器件的电流密度箱线分布图。f, 在横向尺寸为500

×

500 nm²的Pt/h-BN/Pt器件中测得的I-V曲线。

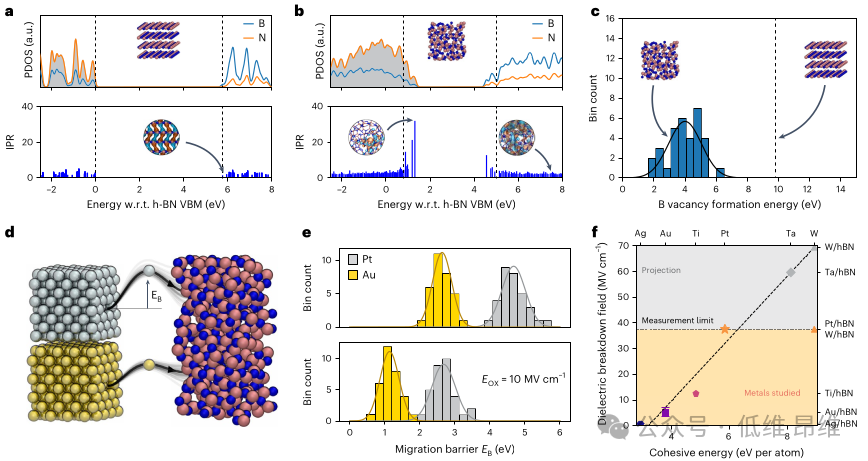

图 4:Pt/h-BN/Pt和Au/h-BN/Au器件中介电击穿的原子级模拟。a, 体相h-BN的投影态密度和IPR(逆参与比)分析。b, 非晶态氮化硼(a-BN)的类似分析。c, h-BN和a-BN中B空位的形成能。d, 金属原子渗透a-BN的示意图。e, 通过DFT获得的渗透势垒直方图(上图)和通过正偏压校正后的结果(下图)。f, CVD生长的h-BN被金属夹层的介电击穿场强与该金属的内聚能的关系图。

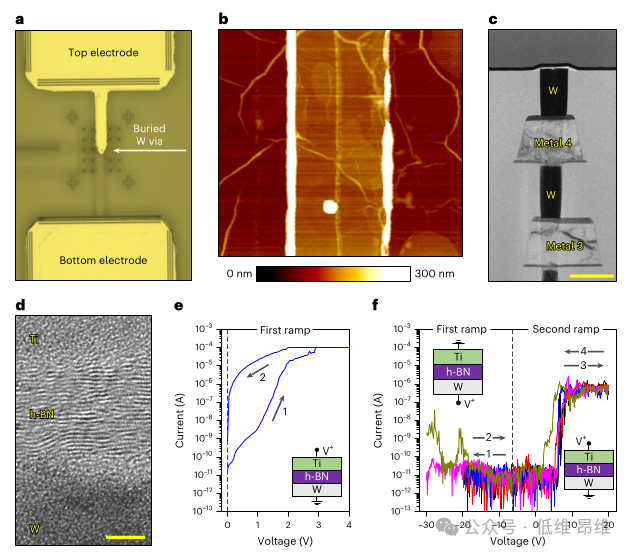

图 5:嵌入在微芯片中的Au/Ti/h-BN/W结构的表征。a, Au/Ti/h-BN电容器的光学显微镜图。b, 原子力显微镜(AFM)图,可以观察到顶部电极、W通孔和h-BN的褶皱。c, Au/Ti/h-BN/W电容器的横截面透射电子显微镜(TEM)图像。d, 芯片上靠近W通孔区域的放大横截面TEM图像。e, 施加于顶部Ti电极的正I-V曲线。f, 施加于五个不同器件底部W电极的正I-V曲线。

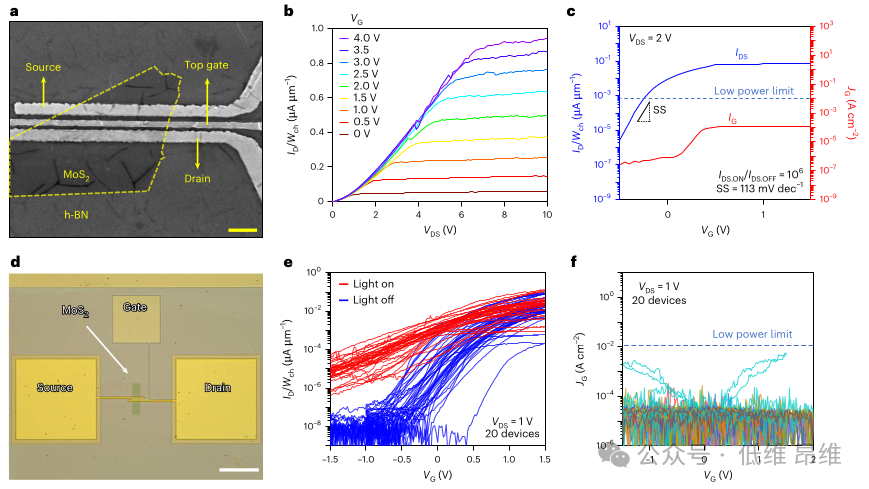

图 6: 具有Pt/h-BN栅极堆栈的 MoS

2

晶体管的形貌和电学特性。a, 具有Pt/h-BN/MoS

2

结构的晶体管的SEM图像。b, c,晶体管器件的输出特性 (b) 和传输特性 (c)。d, 具有Pt/h-BN/MoS

2

栅极堆栈的全CVD晶体管的光学显微镜图像。e,20个如 d 中的器件在黑暗和光照下的传输特性。f,在e中测量的相同20个器件的栅极电流密度与栅极电压的关系。

【总结展望】

总之,本文表明尽管h-BN含有大量原生缺陷,但具有高内聚能的金属电极可使商用CVD生长的2D层状h-BN用作晶体管中的栅极电介质。与Au电极相比,使用Pt电极可将约8 nm厚的CVD生长h-BN的漏电流降低约500倍,而使用W电极则在高达20 V的电压下产生无法检测到的漏电流,在这两种情况下,电极都提供了超过25 MV cm⁻¹的介电强度。进一步优化的Pt/h-BN和W/h-BN堆栈,以及使用其他适合工业应用的高内聚能金属(如TaN或TiN),可能使它们满足CMOS技术的要求。本文提出的方法最终可能有助于加速二维材料在固态微电子器件和电路中的应用。

【文献信息】

Shen, Y., Zhu, K., Xiao, Y. et al. Two-dimensional-materials-based transistors using hexagonal boron nitride dielectrics and metal gate electrodes with high cohesive energy. Nat Electron (2024).