本文内容非商业用途可无需授权转载,请务必注明作者及本微信公众号、微博 @唐僧_huangliang,以便更好地与读者互动。

前一天晚上写了东西,按道理应该休息下,不过我看到唐杰总的微博上有新鲜的资料,手痒痒又想班门弄斧写点东西

…

如果没搞错的话,这些图片有可能来自

AMD

官方

ppt

。看上面的时间点,

7nm

的“

ZEN 2

”下一代

EPYC

服务器

CPU

现在应该有测试样品了,预计明年发布,当然也如果是下半年或者年底都还不算跳票。

首先,我在《

AMD EPYC

官方资料乌龙?谈服务器

CPU

互连效率

》和之前的文章中提到过“胶水封装”,并专门写过一篇应用调优的注意事项《

多级

NUMA

:

AMD EPYC

互连速率、位宽与功耗的关系

》。下一代会怎么设计呢?

轮回:北桥(North Bridge)重生

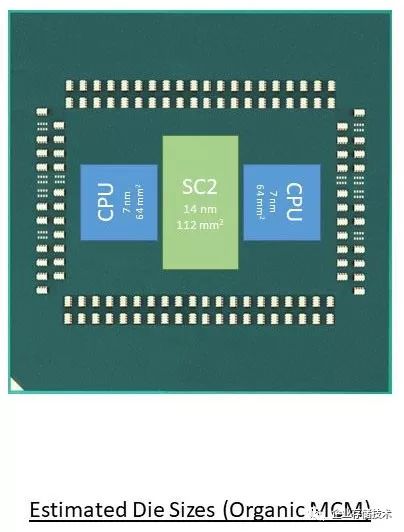

我对芯片面积不是太敏感:)

上图仍然是

MCM

多

Die

封装,不过除了

2

个

7nm

的

CPU Die

之外,

AMD

这个

14nm

的

SC2

(

System Controller

)

似乎又把“北桥”给恢复了。也就是说,最近这些年被集成进

CPU Die

之内的一些东西,又给拿出来了。

这一改变有

哪些利弊

呢?请接着往下看

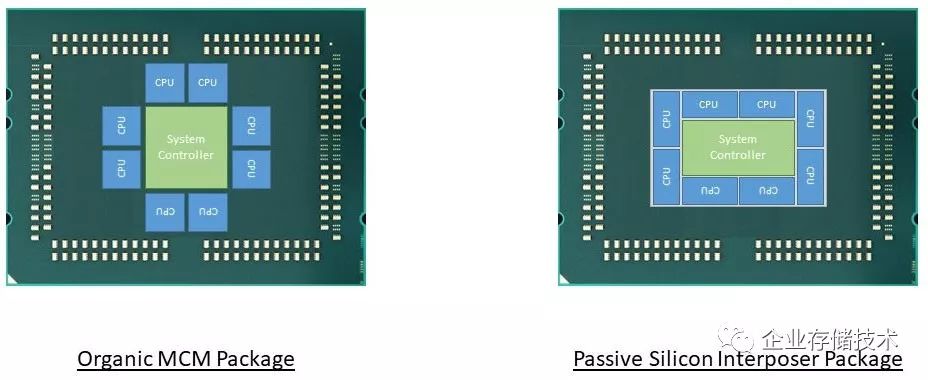

上面右边的

Passive Silicon Interposer Package

封装方式,应该看起来还是一个

Die

,但估计不能使用

2

种不同集成度的制造工艺;那么

AMD

下一代

EPYC

采用的就是左边这种

Organic MCM Package

。

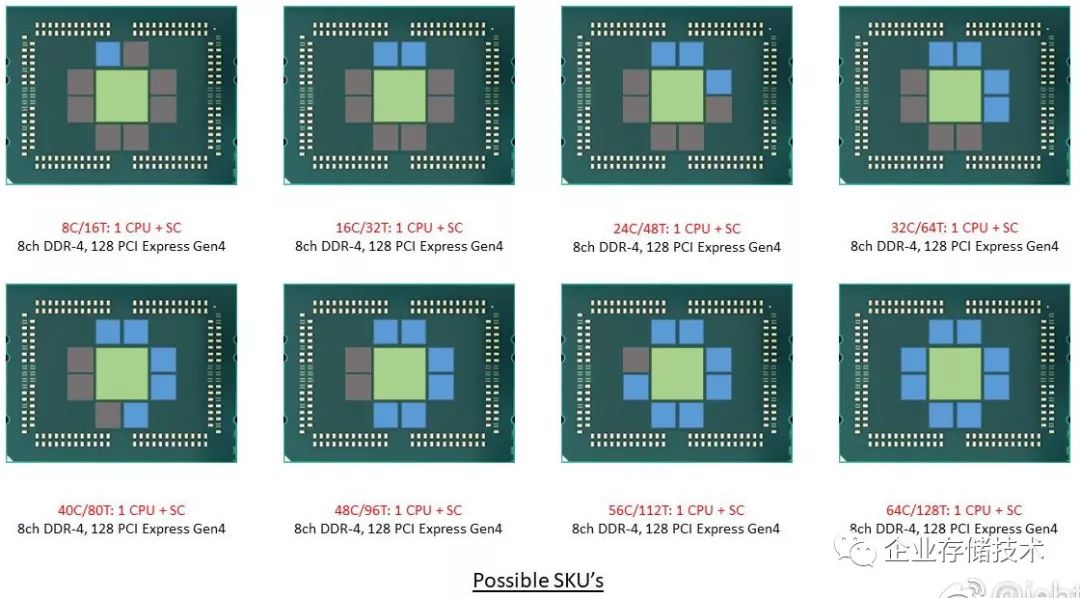

如上图,每个蓝色的

CPU Die 8

个核心(

16

线程),

AMD

可以选择

配置(激活)

1-8

个

Die

来实现

8-64

核

的

CPU

,同时也会带来不同的功耗(主频是另一个影响因素)。

另外,

8

通道

DDR4

内存和

128 lane PCIe Gen4

控制器都是不变的,因为绿色的那颗

System Controller

必不可少。

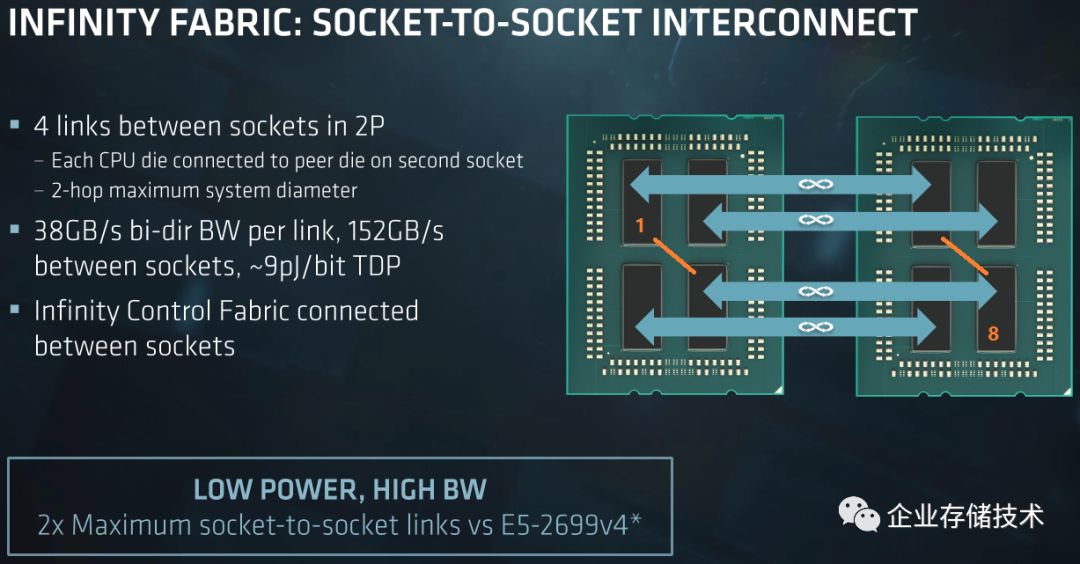

上图为当前的

EPYC

的双

CPU

互连方式,每个

CPU

上的

4

个

Die

各自重定义一个

x16 PCIe lane

用于

Infinity Fabric

,正好是单

CPU 128 lane PCIe

控制器的一半。

下一代

EPYC

在这点上仍然相似。

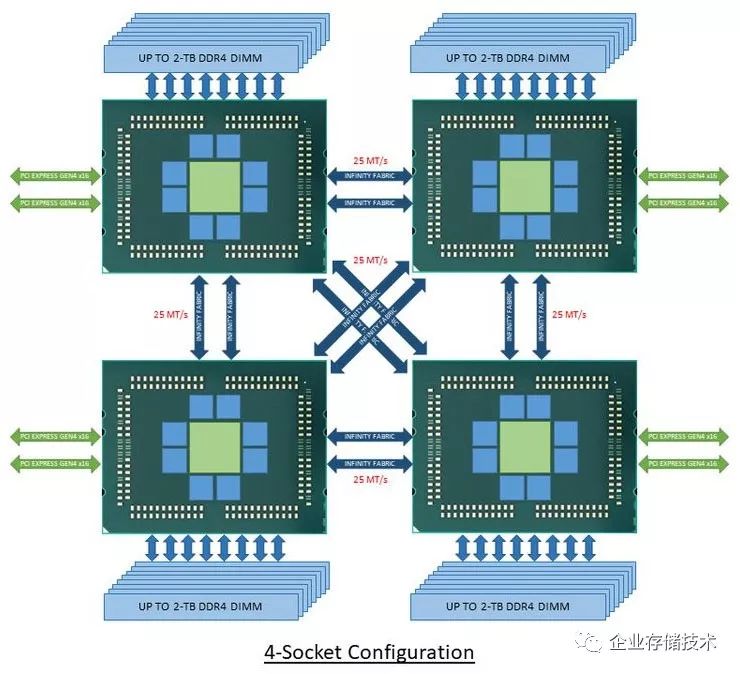

AMD

也要有

4

插槽的配置

了,这个前提是

PCI

控制器集中

在每颗

CPU

上绿色的

SC Die

。

上图中

CPU

之间互连的

25 MT/s

可能是笔误了?

估计是

25 GT/s

吧,就像

IBM Power

的

CAPI

那样(扩展阅读:《

从

Power9

互连技术看

Intel

与

IBM

的生存之道

》)。每

2

颗

CPU

之间相当于都是

2

条

重定义为

Infinity Fabric

的

PCIe x16 I/O

,这样

4

插槽系统每颗

CPU

还剩下

2

个

PCIe x16

,

整机还是

128 lane

。

不同

CPU

插槽之间的内存

NUMA

还是存在的,而具体到每颗

CPU

内部

AMD

可以说摘帽了吧?

片上

SMP

解决

NUMA

问题,不足是?

如上图,左边的

CCX

就是

AMD 8 Core

的

CPU Die

,每个集成

32MB

的

L3 Cache

。内存控制器、

PCIe Gen4

控制器

/Infinity Fabric

插槽间互连

I/O

,以及

IO COMPLEX

(相当于传统南桥

/PCH

)都集成在

System ControllerDie

上。

这样的好处是,

CPU Die

对内存和

PCIe

设备的访问应该是对等了

(相当于片上

SMP

吧),不再有片上

NUMA

的问题;不过,内存和

PCIe

的访问

延时可能不如现在的

Intel

和

AMD CPU

?

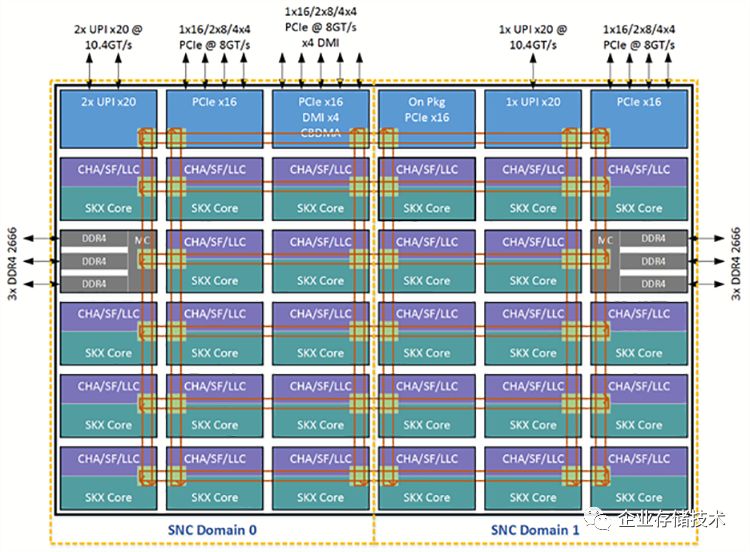

下面简单再看下

Intel Xeon Scalable

(

SP

)的网格互连设计:

当

CPU

核心数增加到一定规模

,

Intel

也不可避免遇到了一颗

CPU Die

上

Sub-NUMA Clustering

的问题。

如上图,左边的一半

Skylake Core

(含

L3 Cache

等)亲近于左边的

2

个

DDR4 2666

内存控制器,被命名为

SNC Domain 0

,其中还包含

2

个

UPI CPU

互连、

2

个

PCIe x16

控制器以及连接

PCH

的

DMI x4

接口等;同理右边那一半区域就是

SNC Domain 1

的资源。

Intel Xeon

也要做

MCM

多芯片封装?

那么未来

Intel

会不会也把

CPU

核心拆分为

2

个

Die

呢?这一点其实在下面的资料中有暗示。

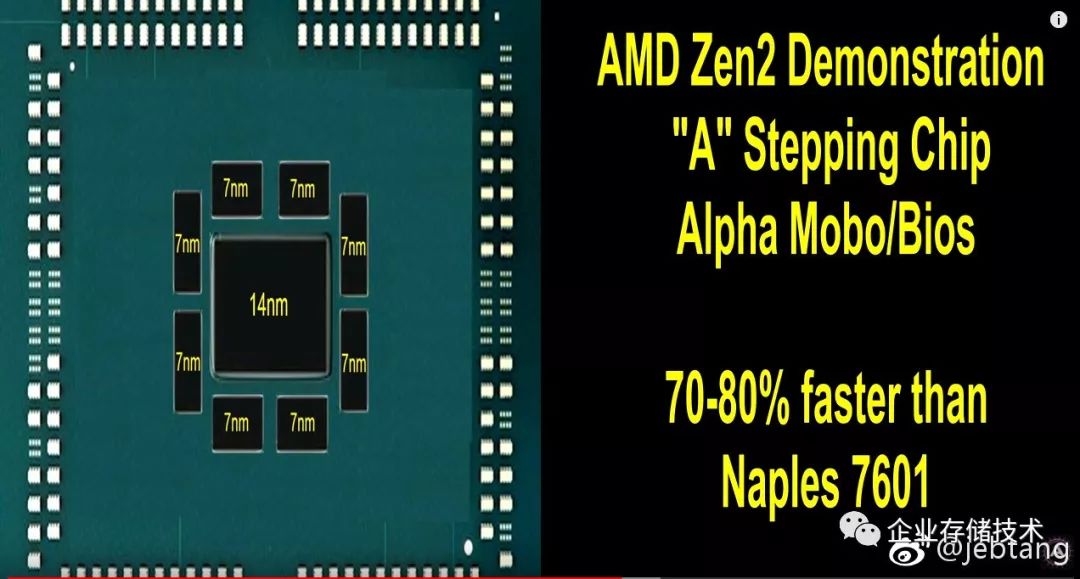

AMD

号称

Zen2

架构比现在代号

Naples

的

EPYC 7601

速度快

70-80%

,当然核心也增加了一倍哦。

我不保证上图一定出自

AMD

的

ppt

:)

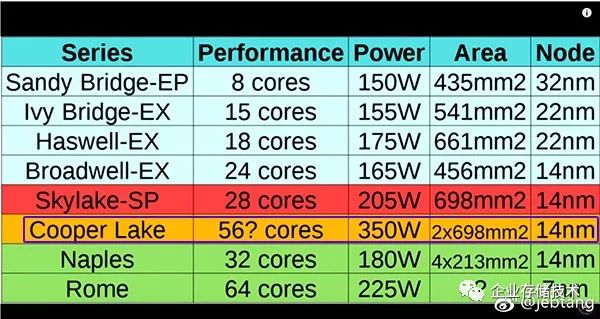

如上图,

AMD

代号

Rome

的下一代

EPYC

由于

7nm

工艺

功耗只上升至

225W

,只是不知道新制程能否在明年内就达到成熟?

据悉,

Intel

将于年底发布的新一代

Xeon SP

(

Cascade Lake-SP

)可能仍将采用

14nm

,并兼容现在的

LGA-3647

插槽和服务器平台。再下一代的“

Cooper Lake-SP/AP

据称依然采用

14nm++

工艺?

2019

年晚些时候或者

2020

年发布,将是

一个原生、一个

MCM

封装

,后者支持

6

条

UPI

总线。”

上图显示多

Die

封装的

Cooper Lake-AP

核心数量也会增加比较多,

要是它能改用

10nm

工艺就好了

。那样

AMD

就不会再写出

56

?

cores

、

350W

、

2x698mm

这样的描述了

…

先写到这里吧,大家有什么意见欢迎拍砖:)

注

:本文只代表作者个人观点,与任何组织机构无关,如有错误和不足之处欢迎在留言中批评指正。

进一步交流

技术

,

可以

加我的

QQ/

微信:

490834312

。如果您想在这个公众号上分享自己的技术干货,也欢迎联系我:)

尊重知识,转载时请保留全文,并包括本行及如下二维码。感谢您的阅读和支持!《企业存储技术》微信公众号:

HL_Storage

长按二维码可直接识别关注

历史文章汇总

:

http://chuansong.me/account/huangliang_storage