作者:Teledyne e2v 公司,Pierre Fereyre,Gareth Powell

I. 引言

早于上世纪九十年代初,有意见认为电荷耦合器件(Charge Coupled Device,CCD)日渐式微,最终将成为“科技恐龙”[1]。如果用索尼公司(Sony)2015年的发布来看待,这个预言好像也有点道理:当时索尼公司正式发布终止量产CCD时间表,并开始接收最后订单。虽然多年前业界已预计这是迟早出现的举措,但是索尼这一发布仍然震惊了专业成像社群[2]。值得一提的是很多工业或专业应用(就是CMOS 图像传感器 (CIS) 的重点市场)到现在仍然基于CCD传感器技术。到底CCD有什么特点优于CIS,使其更具吸引力呢?在发展初期,CCD和CIS两种技术是共存的;后来CCD被视为能够满足严格图像质量要求的高端技术,而同时期的CMOS技术仍然未成熟并受制于其固有噪声和像素复杂性等问题。在这一时期,图像技术仍然以模拟结构为主,而集成图像处理功能(系统级芯片SoC)这一意念还没有被认真考量。基于摩尔定律,技术节点的缩小使得SoC技术从2000年起快速扩展并更具竞争力。现在CIS继续致力改进光电性能,在很多方面都显得比CCD优胜。如果利用文首提到的“进化论”譬喻,其实可以把CIS视作抵过多次自然灾害仍然存活的哺乳类动物,而这个进化历史更是跨越6500万年的史诗式故事!

II. CCD和CMOS:同源异种

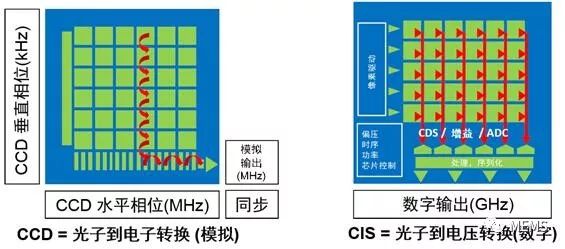

CCD的工作原理是将光子信号转换成电子包并顺序传送到一个共同输出结构,然后把电荷转换成电压。接着这些信号会送到缓冲器并存储到芯片外。在CCD应用中,大部分功能都是在相机的电路板上进行的。当应用需要修改时,设计人员可以改动电路而无需重新设计图像传感器芯片。在CMOS图像传感器中,电荷转换成电压的工作是在每一像素上进行。CMOS图像传感器芯片在像素级把电荷转换成电压,而大部分的功能则集成进芯片。这样所有功能可通过单一电源工作,并能够实现依照感兴趣区域或是开窗灵活读出图像。一般来说,CCD采用NMOS技术,因而能够通过如双层多晶硅、抗晕(antiblooming)、金属屏蔽和特定起始物料互相覆盖等特定工艺实现性能。而CMOS是基于用于数字集成电路的标准CMOS工艺技术生产,再根据客户要求加入成像功能(如嵌入式光电二极管)。

一般的见解是CMOS图像传感器的生产成本比CCD低,因而它的效能也较CCD低。这个假设是基于市场需求的考量而出的,但是其它专业市场的意见却认为两者的技术水平相若,而CCD甚至可能更经济[3]。例如大型主要的航天计划仍然采用CCD元件,原因不单是CCD在小批量和低成本的考量下在工艺级实现性能优化,还有是长期稳定供货的需求考量。同样地,基于高端CCD的解决方案在科学成像市场也有主流占有率,而且还有一些新产品在开发阶段。情况就是恐龙进化成飞鸟,而它们大部分都能够提供优秀的成像功能……

CMOS的拥有经改进的系统复杂性,因为它基本上是嵌入了如模数转换、相关双采样(CDS)、时钟生成、稳压器等系统级芯片(System-on-Chip,SoC)结构,或是图像后处理等功能,而这些以前都是应用系统级设计才有的功能。现在的CIS通常是依照从180 nm到近期65 nm的1P4M (1层聚酯,4层金属) 工艺生产,允许像素设计加入非常高的转换因子,便于结合列增益放大。这使得CMOS的光反馈和光敏感度一般都比CCD为佳。相较于CMOS,CCD芯片的衬底偏压稳定性更好且芯片上的电路更少,所以拥有更显着的低噪优势,甚至达到无固定模式噪声的水平。

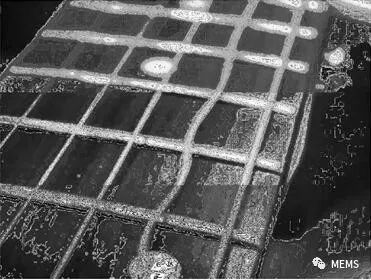

图1 CCD和CMOS结构比较

表1 CCD和CMOS特点比较表

另一方面,CIS有较低采样频率,可以减小像素读出所需要的带宽,因而瞬时噪声也较小。快门会同时对阵列上的所有像素进行曝光。但是CMOS图像传感器采用这一方法的话,由于每像素需要额外的晶体管,反而占用更多像素空间。另外,CMOS每一像素拥有一个开环输出放大器,而因着晶圆工艺的差异,每一放大器的补偿和增益会有所变化,使高或暗的不均匀状况都比CCD传感器差。相对于同级的CCD,CMOS图像传感器拥有较低的功耗,而芯片上其它电路的功耗也比CCD经优化模拟系统芯片匹配的解决方案来得低。取决于供货量并考虑到CCD导入外部相关电路功能的成本,CMOS的系统成本也有可能低于CCD。表1总结了CCD和CMOS的特点,有些功能有利于一种或其他技术,所以毋需完全分割整体性能或成本。不过,CMOS的真正优势是通过系统级芯片(SoC)方式实现导入灵活性,以及其低功耗特点。

III. 关于噪声性能的常见误解

视频成像链的带宽必需小心调整,以便最小化数字化阶段的读出噪声。可是这一带宽也必需足够大以防止图像出现其他缺陷。这一惯常做法也适用于CCD和CMOS。带宽的最小阈值是信号由采样达到足够接近理想水平所需要的时间决定。诱发性错误应处于接近最低有效位(Least Significant Bit,LSB)的可忽略水平。要决定所需要的带宽,可以应用下面的准则:

把放大链带宽fc,信号频率fs和N(即ADC解析率)置入算式计算。例如N=12时,数值则是:

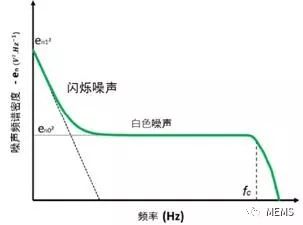

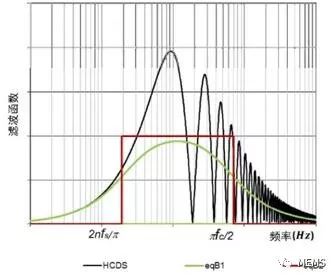

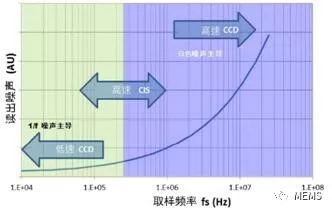

噪声最由两个因素造成:1/f闪烁噪声和热噪声(见图2)。闪烁噪声是大自然中常有的噪声,而它旳频谱密度和地球自转速度、海底水流、天气以至气候现象等活动相关。研究报告显示普通蜡烛的闪烁速率是1/f 。在MOS器件和放大链各元素中,闪烁噪声则是技术工艺误差生成的缺陷,使电荷被困于栅极氧化物内所造成的结果。电荷进出这些“陷阱”,造成晶体管通道内的电流不稳定[6],故又称「随机电报噪声」(Random Telegraph Noise,RTS)。利用洛伦兹数学模型(Lorentzian mathematical model)可以形容每一个“陷阱”的共振行为,而模型的总和(即MOSFET通道表面范围的所有“陷阱”总和)在1/f频谱上展示时,会全完符合具体噪声的频谱密度。结果显示,1/f波幅与MOSFET通道表面面积成反比──而不是完全直观。

图2 频谱噪声密度

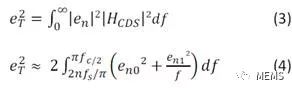

要去除或减小CIS上的放大器共模差异,浮点的重置噪声以至晶体管技术分散,视频通道通常集成一个相关双采样(CDS)级。这一元素把视频信号传送函数依照下面的算式进行转换:

在算式中,fs是采样频率,n是CDS因子(通常n=2)。如图3显示,取决于采样频率,这一滤波或多或少地去除1/f噪声频率成分,尤其是当采样频率fs很高的时候显著(换句话说,电荷进出“陷阱”的动作将慢于CDS频率)。HCDS滤波器结合放大链的低通滤波器可以简化为一个如图3所示的等效带通滤波器。图中的eqBP1 对应一个一级带通滤波器。这裡eqBP1的噪声频谱函数要除以2,以得到一个带有HCDS函数的等效集成噪声功率。eqBP2 是eqBP1的陷波估算值。要取得集成噪声功率,eqBP2 的上限和下限分别按照下列算式进行倍增:

图3 噪声滤波函数

在图2和图3所示的一般状况下,噪声性能可依照下面的算式展示:

把算式(1)和(4)合并后,得出总体集成读出噪声估算值如下:

有关算式经验证跟数字仿真结果相当匹配。CCD的读出噪声可达到非常低水平,适合如天文或科学成像,这些应用领域的读出频率可以非常低。系统设计包含有最小频带宽的电子元素,以避免集成进信号的不稳定时脉。在这些应用中,噪声的1/f元件有主导地位。在高速视频应用中,高噪声使得信噪比显著变差。从多个不同CCD视频相机录得的具体噪声表示状况数据,确认了有关理论 [5] 。CMOS 图像传感器的列式平行读出布局(见图1)在这一方面提供优势。阈值读出频率除以列数,再与CCD数值比较。在这里,CIS的读出噪声主要由1/f数值主导。这有助于进一步改进CMOS技术在成像方面的性能。近期的结果显示,CIS可提供达到1E-或更低范围的优秀噪声性能。

图4 读出噪声作为fs的函数

IV. MTF 和 QE:成像质量的支柱

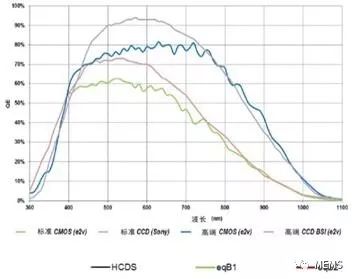

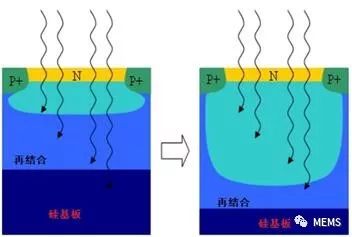

量子效率(Quantum efficiency,QE)是直接影响图像传感器光电性能的因素,因为光电转换效率的任何损耗都会直接减低信噪比(Signal-to-noise ratio,SNR) 。它的影响是两方面的,因为当散粒噪声(信号的平方根)是主要噪声源时,QE不单是信噪比的被除数(信号),同时也是除数(噪声)。在这一点之上,CCD和CMOS处于同一水平,可是CCD在QE改进方面累积有多年的技术工艺优化,而在CIS的QE改进发展相对较迟。基于硅物质的物理特性,较长的波长能穿透光敏转换地带,所以会使用厚的外延材料来增加上红色和近红外线波长的QE。根据比尔朗伯定律(Beer-Lambert law),被吸收的能量是与介质的厚度成指数关係。高端应用的CCD利用较厚的硅物质和背照(Back Side Illumination,BSI)工艺以恢复高宽带QE和近红外(near infrared,NIR)敏感度,因而拥有优势。

图5 QE指标

隔行传输CCD(Interline Transfer CCD,ITCCD)是基于特定的生产工艺,导入所谓的“垂直溢漏”(Vertical Overflow Drain,VOD)或“垂直抗晕”(Vertical Anti-blooming,VAB)功能。VAB开发于1980年代初期,具有非常好的性能,但缺点是会减低红色的反馈并拒绝频谱中的NIR部分。

图6 深耗尽方法

因为这个原因,ITCCD不能从BSI中获益。而高端CCD因为使用垂直抗晕工艺,所以没有这一限制。而CMOS也具有同一特点:在薄的感测层上,因为电荷不会在像素之间渗透,所以没有串扰的缺点。结果是ITCCD和标准CIS都能够实现良好的空域解析度或调制转换函数(Modulated Transfer Function,MTF) 。要增加NIR部份和敏感度,需要显著增加物料厚度,但是厚物料会增加光电串扰,引致MTF衰减。成像质量是MTF和QE的综合结果(即所谓的检测量子效率Detective Quantum Efficiency,DQE),所以必需同时考量空域和时域因素。图6显示利用硅掺杂方法恢复MTF的深耗尽(deep depletion)光电二极管。一般来说,CIS使用类似集成电路的常用技术(特别是DRAM/内存工艺)生产,所以不会牵涉上述的特定工艺配方。不过近期的技术研究文章展示适用于CIS的特定工艺导入方案,能实现出色的QE改进甚至相对接近高端CCD的水平(见图5) [9][10]。最新的CMOS技术趋势可说是突飞猛进,引进了如导光板、深槽隔离(Deep Trench Isolation,DTI)、埋藏微透镜,以及在光敏范围下嵌入包含像素晶体管的迭层芯片等技术。

V. 固有缺陷

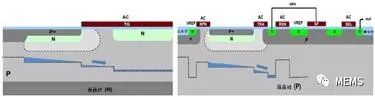

“嵌入式光电二极管”(Pinned Photodiode,PPD)或“空穴堆积二极管”(Hole Accumulation Diode,HAD)最初开发目的是消除延迟并把全部电荷从光电二极管转移到ITCCD寄存器[12]。CMOS图像传感器的一个重大发展是在2000年代初期引进ITCCD光电二极管结构[11],如图7所示。在CMOS中,像素结构多数以每像素的晶体管数目来表示。大部分 CMOS图像传感器倾向使用电子卷帘快门(electronic rolling shutter),这有助于集成并只需少至三个晶体管(3T)就能实现。虽然有结构简单的优点,3T像素结构的缺点是电路来自kT/C(或温度)噪声的像素生成时域噪声会较大,而且不能轻易消除。

图7 ITCCD和5T CMOS图像对比图

嵌入式光电二极管最初引进到CIS以去除来自浮动扩散重置的噪声,后来并引进到四晶体管像素(4T)结构中。4T结构进行相关双采样(CDS)以消除重置瞬时噪声。这一结构也允许晶体管在像素间共用布局,以便于把每像素的有效晶体管数目减到两个或更少。事实证明,每像素的晶体管数目减少,能够空出更多范围供光敏部分或填充因子去更直接地把光线耦合到像素上。不过如图8所示,在获取视频或包含快动作的图像时,ERS会导致更多图像变形。PPD会在第二级时工作,以进行全局快门(GS)获取。它能够去除ERS伪影并进一步消除时域噪声、暗电流和固定模式噪声。接近PPD的第五个晶体管(5T)的功能是排除过多的电荷并调整重迭模式的集成时间(在集成时读出)。

图 8 图像瑕疵:CMOS ERS变形

全局快门(GS)模式一般配合ITCCD使用,但在某些状况下会对弥散现像敏感。

图9 图像瑕疵:CCD弥散

弥散是在电荷转移时出现的现像,会在影像上产生直线如图9。这瑕疵在高反差图像上尤其显著,但不应把它和相似的光晕现像混淆。最常用的解决方案是导入帧行间转移(Frame Interline Transfer,FIT)CCD结构,而FIT也拥有较高视频速率的优点。与CMOS等效的弥散参数是全局快门效率(Global Shutter Efficiency,GSE),有时也称为寄生光敏度(Parasitic Light Sensitivity,PLS),是对应于传感节点到光电二极管的敏感度比例。ITCCD的GSE值一般介乎于-88dB到-100dB[13],在CMOS则是-74dB到-120dB甚至是3D迭层结构的-160dB[14] 。利用先进定制像素微镜片(如zerogap)可在从改进波长反馈的敏感度到减小CMOS像素上的二极管所造成的填充因子损失方面实现显著的分别。它也是改进GSE性能的主要因素。

VI. CMOS成像技术的未来

CCD技术特别适合时间延迟积分(Time Delay Integration,TDI)领域。TDI(在扫描场景时,电子同步的积分和累加)的导入相对直接,只需要一个电荷转移器件就可以完成。这技术最初用于信噪比最大化,然后用于CIS CCD以保存良好的图像定义(MTF)。近年多个于模拟区域(电压)[18]或数字区域复製信号累加的尝试,为CMOS TDI开拓新的发展方向。不论在太空地面观测或是在机器视觉方面,CCD延迟积分结构的低噪声和高敏感度性能都广受欢迎。不过现时最令人期待的发展是基于CMOS工艺、但拥有CIS CCD的优点以及电荷转移寄存器结合行式ADC转换器的技术[17] 。虽然有长足进步,CMOS图像传感器的敏感度在光线非常微弱应用(如只有几十微流明的环境)仍然受限于读出噪声。使用电子倍增技术的EMCCD[15] 显示出在降噪方面的巨大潜力,因而受到科学成像市场的注意。一般来说,就如CCD被CMOS传感器取代一样, EMCCD也有潜力朝着电子倍增CMOS(electronmultiplying CMOS,EMCMOS)的方向发展[20]。一如EMCCD,EMCMOS计划改进光线非常微弱应用中的图像质量,以配合科学或监视方面的应用。CMOS技术有助于实现更小更具智能的系统、降低功耗,以减低量产的成本(即所谓的SWAP-C方法)。电子倍增的原理是在读出链任何加入任何噪声前为信号进行增益,使得噪声被增益摊分,以改进信噪比。基于CCD原理,信号会以电子包的形式传送,然后在读出之前共同对每一个像素进行倍增。CMOS的信号是在电压域,因而倍增工作必需在源跟随晶体管把噪声加进信号并传送到浮点之前完成[16]。

随着3D成像的流行,需要物件深度的信息,飞行时间(Time-of-Flight,ToF)技术在这一方面派上用场。ToF的原理是在传感器平面上设置人工脉冲光源并发射出去,然后把反馈的反射波段用于相关函数计算来得出距离。这一技术于1995年于 “锁定”CCD中首次提出[21]。而ToF在CMOS的应用则是由CCD像素的启发而来[22]。另一方法则是使用电流辅助光子解调器(Current Assisted Photonic Demodulators,CAPD)测量深度。两种方法都实现了工业3D传感器的量产并实现了一系列的应用如计算人数、安全监控、计量学、工业机器人、手势辨识和先进汽车驾驶者辅助系统(ADAS)等。这是都是CCD技术衍生的意念成功过度到CMOS作改进,再实现工业应用大规模导入的典型例子。

CMOS技术导入也衍生出新的应用范围。举个例子,跟CCD在1980年代在专业相机领域替代现像管(vidicontubes)相似,单光子雪崩二极管(Single- Photon Avalanche Diode,SPAD)原来的开发目的是作为光电倍增管(Photomultipliertubes,PMT)的固态替代产品。SPAD基本上是在所谓的盖革模式(Geiger mode)中,依照击穿模式上的反压进行偏置的p-n 结。不过这结构十分不稳定,任何能量改变都会导致雪崩效应。这一特点被用于单光子感测。通过在SPAD和输入电压之间导入一个简单的电容元件,利用被动抑制原理开闭雪崩,或使用嵌入式MOSFET通道启动主动抑制原理达到同一目的。这样就可以製作代表量子事件的数字信号。根据原理,SPAD一个基于简单结构的CMOS技术,无需用于图像传感器的专门工艺。不过因为它需要复杂的电路,SPAD阵列的工作也较为复杂。跟光子的到达一样, SPAD的引发和事件记数依定义是非同步的。CMOS技术因而是不二之选。例如这就能够非常快速地启动扫描像素阵列,以确认已转换的像素。这些帧组合后就能製作一个视频序列 [23]。

VII. 总结

早期一些宣称CCD年代终结的文章已被视为预言[1],只是实际的过渡时间比预计的长许多。另一方面开发用于CMOS图像传感器的图像结构种类和创新性都大大超越前人想像。随着晶体管蚀刻工艺缩小化和CMOS生产技术演进,这些创新都变得可行。大型工业成像厂商除了价格,还继续在光电性能方面进行竞争。现在的使用者已经不是单单在乎于拍照,而是获取人生中各个重要时刻,因而期待不论在任何光线状况下都能拍出完美的照片。工业应用也因着这些改进,在其它一般范围上得益。越来越多视觉系统也基于消费者市场趋势而调整其图像传感器要求,图像缩小就是一个例子。而高速处理能够提升高成本生产机器的产量并实现自动化工艺和检查,所以也是一个重要的经济因素。新的应用正把传感器推向性能极限并不允许图像内有更多噪声,推动了单光子成像技术。除了简单的摄影和显示,3D增强现实技术也用尽了CMOS技术的所有潜能,提供另类的视觉空间体验。一如地球上的主要物种,CMOS图像传感器已经大大进化并适应其周遭环境。

参考文献(REFERENCES)

[1] Active pixel sensors: Are CCD dinosaurs? ER Fossum IS&T/SPIE's Symposium on Electronic Imaging: Science and Technology, 2-14A.

[2] http://www.vision-systems.com/articles/2015/03/sony-rumored-to-discontinue-production-of-ccd-sensors.html

[3] CCD vs. CMOS, Dave Litwiller, Photonics Spectra, 2001

[4] Determination of the optimal electrical bandwidth in CCD- and CMOS-based image detector applications, Robert H. Philbrick, SPIE 5499, Optical and Infrared Detectors for Astronomy, 2004

[5] CMOS vs. CCD: Changing Technology to Suit HDTV Broadcast, Lester J. Kozlowski, 2003

[6] Fundamental performance differences between CMOS and CCD imagers: Part 1, James Janesick et al., SPIE 6276, High Energy, Optical, and Infrared Detectors for Astronomy II, 62760M, 2006

[7] A 0.7 e-rms Temporal Readout Noise CMOS Image Sensor for Low Light Level Imaging, Y. Chen et al., IEEE International Solid-State Circuits Conference (ISSCC), 2012.

[8] http://www.caeleste.com/caeleste_publications/2011CNES/20111207_CNES_caeleste_presentation.pdf

[9] L²CMOS Image Sensor for Low Light Vision, Pierre Fereyre et al., International Image Sensor Workshop, 2011

[10] Night Vision CMOS Image Sensors Pixel for SubmilliLux Light Conditions Amos Fenigstein, International Image Sensor Workshop, 2015

[11] A Review of the Pinned Photodiode for CCD and CMOS Image Sensors Eric R. Fossum, et al., IEEE Journal Of The Electron Devices Society, Vol. 2, no. 3, may 2014

[12] No image lag photodiode structure in the interline CCD image sensor, N Teranishi et al., Electron Devices Meeting, 1982 International (Volume:28 ), 1982

[13] http://www.sony.net/Products/SC-HP/new_pro/may_2014/icx825_e.html

[14] A 3D stacked CMOS image sensor with 16Mpixel global-shutter mode and 2Mpixel 10000fps mode using 4 million interconnections, Symposium on VLSI Circuits (VLSI Circuits), T. Kondo et al., pages C90 - C91, 2015

[15] M. S. Robbins and B. J. Hadwen, “The noise performance of electron multiplying charge-coupled devices,” IEEE Transactions on Electron Devices, vol. 50, no. 5, pp. 1227–1232, May 2003

[16] Electron Multiplying Device Made on a 180 nm Standard CMOS Imaging Technology, Pierre Fereyre et al., International Image Sensor Workshop, June 2015

[17] First Measurements of True Charge Transfer TDI (Time Delay Integration) Using a Standard CMOS Technology, F. Mayer et al., International Conference on Space Optics, 2012

[18] CMOS long linear array for space application G. Lepage, Proc. SPIE 6068, Sensors, Cameras, and Systems for Scientific/Industrial Applications VII, 606807, 2006)

[19] Time-Delay-Integration Architectures in CMOS Image Sensors G. Lepage et al., IEEE Transactions On Electron Devices, vol. 56, no. 11, November 2009

[20] R. Shimizu and Al., “A Charge-Multiplication CMOS Image Sensor Suitable for Low-Light-Level Imaging” IEEE Journal of Solid-State Circuits, vol. 44, no. 12, pp. 3603-3608 December 2009

[21] The lock-in CCD-two-dimensional synchronous detection of light, T. Spirig, P. Seitz et al., IEEE Journal of Quantum Electronics, Vol. 31, Iss. 9, p. 1705 – 1708, Sep 1995

[22] Demodulation pixels in CCD and CMOS technologies for time-of-flight ranging Robert Lange et al., Proc. SPIE 3965, Sensors and Camera Systems for Scientific, Industrial, and Digital Photography Applications, 177 (May 15, 2000)

[23] 320 x 240 Oversampled Digital Single Photon Counting Image Sensor N. AW. Dutton, VLSI Circuits Digest of Technical Papers, 2014

延伸阅读:

《摄像头模组产业市场和技术趋势-2017版》

《汽车MEMS和传感器市场及技术趋势-2017版》

《CMOS图像传感器产业现状-2017版》

《3D成像和传感-2017版》

《非制冷红外成像技术与市场趋势-2017版》