该文章介绍了韩国成均馆大学Jin-Hong Park团队通过使用电子束处理WSe2通道,开发出具有W形电流-电压特性的WSe2同质结器件,这些器件展示了负微分跨导(NDT)特性(W-FETs)。研究表明,这些器件可实现单输入和双输入的三值逻辑门,对于多值逻辑计算具有潜力。

数据生成的快速增长要求计算能力的提升,传统的基于CMOS的二进制计算范式正面临缩放和功率密度的限制。多值逻辑(MVL)计算提供了一个潜在的解决方案,通过提高信息密度、减少器件数量和简化布线来实现。

Jin-Hong Park团队通过电子束处理WSe2通道开发出具有W形I-V特性的WSe2同质结器件,这些器件展示了NDT特性(W-FETs)。这些器件实现了功能完备的三值逻辑门,包括T-NAND、T-AND、T-NOR和T-OR逻辑门,并解决了多值逻辑计算中的噪声问题。

该研究扩展了三种类型的三值反相器设计,这些反相器与T-NAND和T-NOR一起形成了功能完备的三值逻辑。基于实验数据的详细分析和仿真验证了所提逻辑门的功能性,证明了具有W形传输曲线的器件在三值计算中的潜力。

该研究为三值计算提供了一种新的技术路径,具有潜在的应用价值。相对于传统的基于CMOS的MVL电路,该研究提出的器件具有更简单的结构和制造过程,能够执行任何三值逻辑操作。

为了方便各位同学交流学习,解决讨论问题,我们建立了一些微信群,作为互助交流的平台。

2.告知:姓名-课题组-研究方向,由编辑审核后邀请至对应交流群(生长,物性,器件);

欢迎投稿欢迎课题组投递中文宣传稿,免费宣传成果,发布招聘广告,具体联系人:13162018291(微信同号)

研究背景

数据生成的快速增长要求计算能力的提升。传统的基于互补金属氧化物半导体(CMOS)技术的二进制计算范式,经过几十年的持续微型化CMOS晶体管,已满足计算需求。然而,CMOS技术正面临缩放和功率密度的限制,并且受到其逻辑状态二进制性质的制约,限制了信息密度。多值逻辑(MVL)计算提供了一个潜在的解决方案,通过提高信息密度、减少器件数量和简化布线来实现。例如,当从二进制过渡到三值逻辑时,系统复杂度预计将降低至63.1%。然而,基于CMOS的MVL电路由于CMOS晶体管固有的二进制性质,仍然需要大量组件,这减少了MVL计算的优势。

负微分跨导(NDT)器件已成为多值逻辑计算,特别是三值逻辑系统中的有前景的候选技术。为了实现任意三值运算,必须拥有功能完备的三值逻辑门,而目前的NDT技术尚未实现这一目标,这对更高层次电路设计构成了关键限制。此外,NDT器件通常依赖于异质结,这使得制造过程变得复杂,并且由于引入额外的材料和界面,可能影响器件的可靠性。

有鉴于此,近日

韩国成均馆大学的Jin-Hong Park团队

提出了可以通过电子束处理WSe2通道的部分区域,开发了具有W形电流-电压(I-V)特性的WSe2同质结器件,这些器件展示了负微分跨导(NDT)特性(W-FETs)。研究表明,电子束可以通过操控硒原子,精确调节WSe₂的功函数,从而控制W-FET的I-V曲线。该器件的W形I-V曲线具有递减和递增的电流区域,可实现单输入和双输入的三值逻辑门。团队还设计了低器件数、高摆幅操作的三值三值NAND(T-NAND)、三值AND(T-AND)、三值NOR(T-NOR)和三值OR(T-OR)逻辑门,并有效减少了输出信号变化,解决了多值逻辑计算中的噪声问题。此外,本研究还扩展了三种类型的三值反相器设计,这些反相器与T-NAND和T-NOR一起,形成了功能完备的三值逻辑。通过基于实验数据的详细分析和仿真,验证了所提逻辑门的功能性,证明了具有W形传输曲线的器件在三值计算中的潜力。

图文介绍

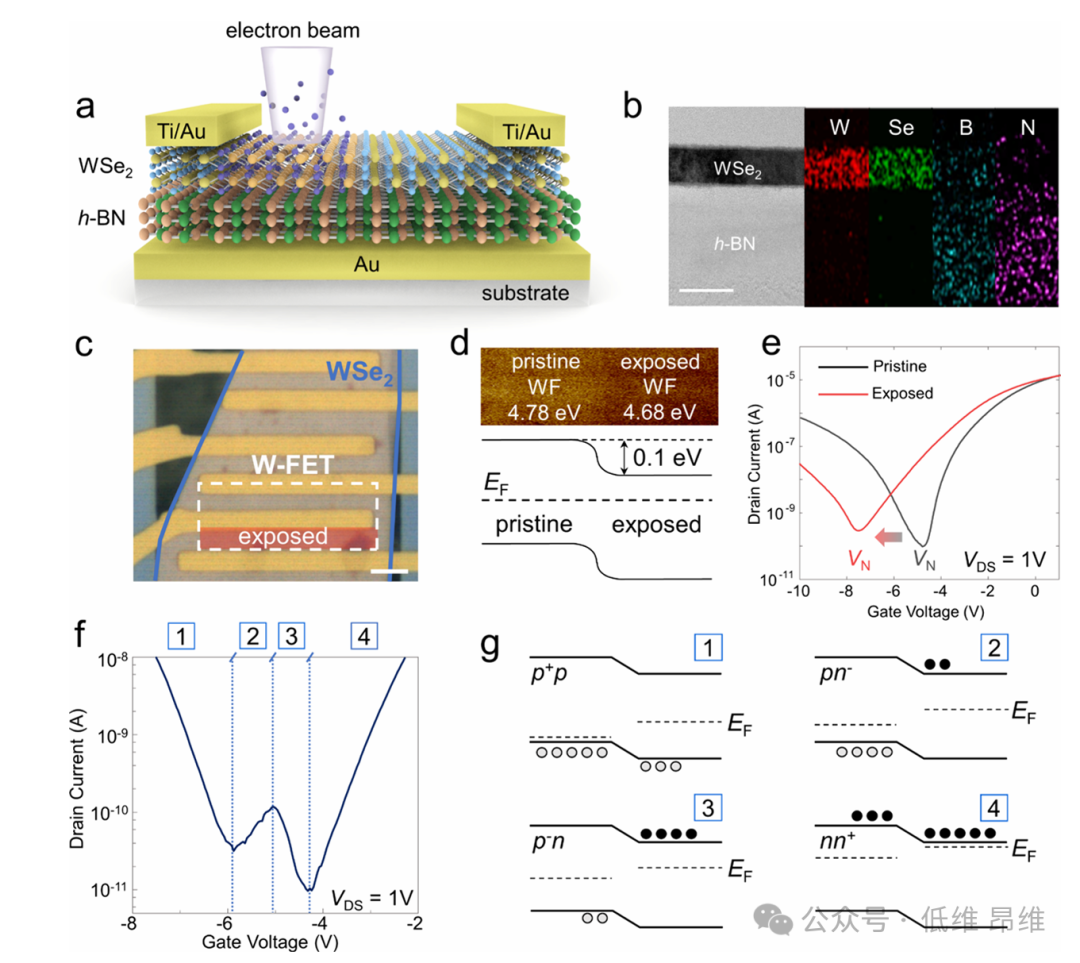

图1.设备结构及工作原理

:(a) W-FET的示意图。(b) W-FET的横截面透射电子显微镜(TEM)图像(左),以及与TEM图像对齐的W、Se、B和N原子的能谱扫描(EDS)元素分布图。比例尺:50 nm。(c) 代表性W-FET的顶部光学显微镜图像,带有多个源/漏电极。比例尺:5 μm。(d) 经部分电子束曝光后的W-FET通道的KPFM功函数(WF)映射图,并提取了未曝光和曝光区域的功函数值。下方的能带图示意性地展示了W-FET通道在平衡状态下的能带对齐情况。(e) 从W-FET的未曝光和曝光区域分别获得的传输I-V特性。(f) W-FET在正向偏压下的代表性W形传输I-V特性,并标出了操作区域。(g) 在施加栅极和漏极偏压下,对应于(f)中四个操作区域的能带示意图。

此图展示了W-FET器件的详细表征,从其示意结构到操作特性。TEM图像和元素映射提供了材料组成的详细信息,而KPFM功函数映射和传输I-V曲线则突出了通过电子束处理如何调节器件性能。能带图为理解器件在不同偏压条件下的工作原理提供了理论依据,支持其在三值逻辑系统中的潜在应用。

图2.

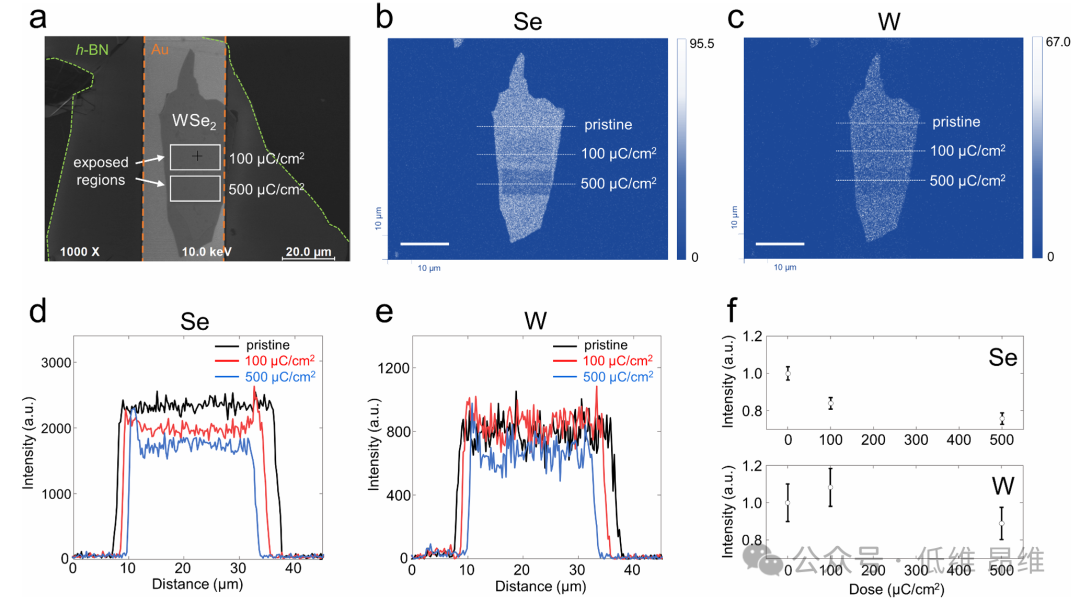

电子束处理的效果

:(a) WSe2在100和500 μC/cm²电子束剂量下,位于h-BN/Au结构上的扫描电子显微镜(SEM)图像,并标出了暴露于电子束剂量的区域。(b, c) 电子束曝光后,Se(b)和W(c)原子的俄歇电子能谱(AES)强度图。白色虚线表示扫描线路,沿这些线路记录了(d)和(e)中的强度剖面。比例尺:20 μm。(d, e) 沿(b)和(c)中标出的扫描线,Se(d)和W(e)原子的AES强度剖面图。(f) 相对于原始区域,Se(上图)和W(下图)原子的AES信号强度随电子束剂量变化的平均值。误差条表示均值的标准偏差。

此图展示了在不同电子束剂量下,WSe2样品中的Se和W原子分布变化。通过SEM图像、AES强度映射和强度剖面,可以清晰看到电子束处理对材料的影响,并通过量化的AES信号强度变化分析,揭示了电子束剂量对WSe2中Se和W元素浓度的影响。

图3,电子束参数对W-FET特性的可调性

:(a) 代表性WSe2场效应晶体管(FET)阵列的顶部光学显微镜图像。比例尺:10 μm。(b) 电子束照射前后WSe2的开尔文探针力显微镜(KPFM)功函数(WF)映射图。红色矩形区域表示获取(c)中WF剖面的特定区域,白色箭头表示扫描方向。比例尺:5 μm。(c) 电子束曝光前后从(b)中标出区域提取的KPFM WF曲线。(d) 60 μC/cm2和90 μC/cm2剂量下WSe2 WF随照射次数的函数。(e) WSe2 WF随电子束照射剂量的函数。(f) WSe2场效应管在不同电子束照射剂量下的转移曲线,显示随着剂量的增加V

N

负位移。

此图展示了WSe2场效应晶体管在不同电子束曝光条件下的功函数变化以及电子束处理对器件性能的影响。通过KPFM功函数映射和传输特性曲线,可以观察到电子束处理在局部区域引发的功函数变化,进一步揭示了电子束曝光剂量与器件性能之间的关系,特别是在WSe2 FET中的V

N

偏移。

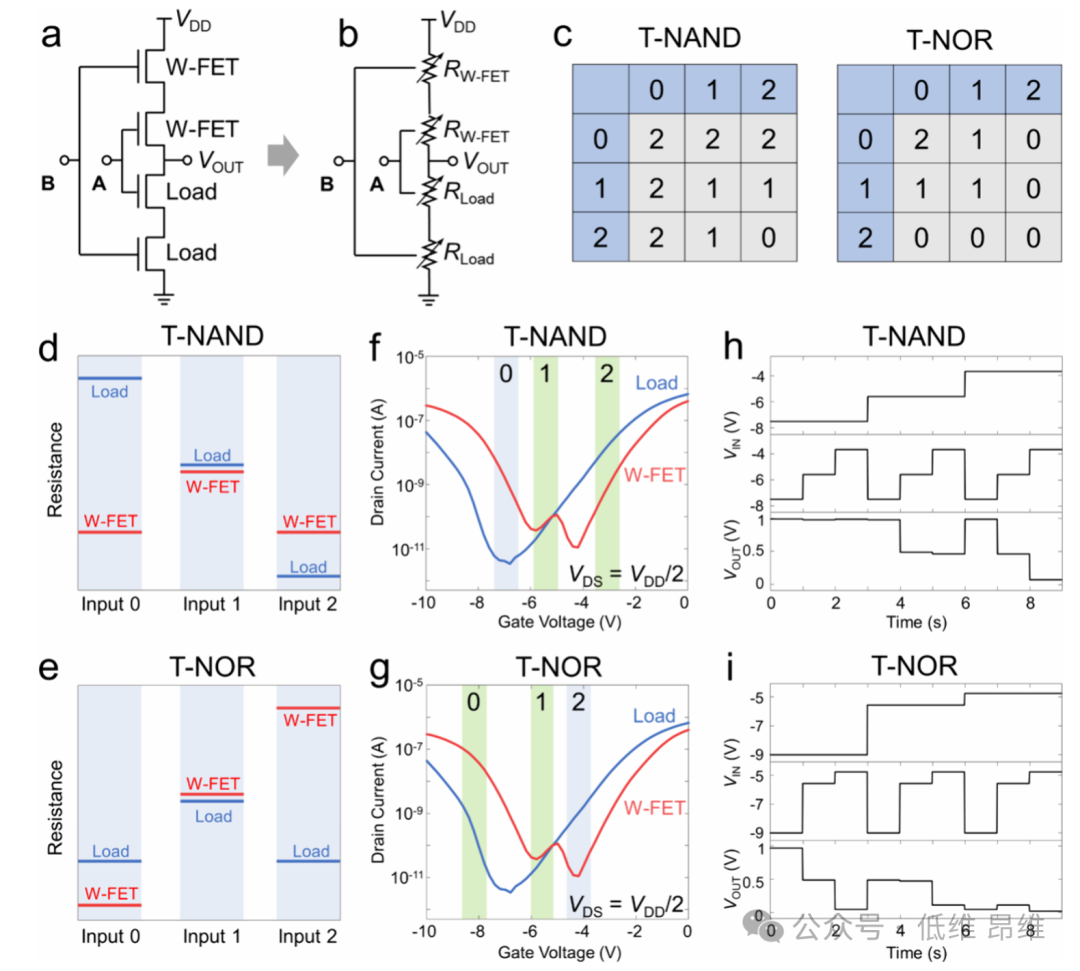

图4,功能完备的三值逻辑门集

:(a, b) 两输入三值逻辑门的电路配置示意图(a)及其表示为由四个可变电阻串联组成的分压器(b)。 (c) T-NAND和T-NOR逻辑门的真值表。(d, e) 使用(a)中的电路配置,T-NAND(d)和T-NOR(e)逻辑门在输入0、1、2下,所需负载FET和W-FET的近似电阻水平的图示。(f, g)在T-NAND (f)和T-NOR (g)逻辑门的情况下,W-FET和负载在漏源电压(VDS)为VDD/2的情况下,终端a的转移I - V曲线。转移曲线对应于施加A = 1, B = 2 (f)或施加A = 1, B = 0 (g)时的状态。(h, i) 在不同输入条件下,T-NAND(h)和T-NOR(i)逻辑门的性能表现。

此图展示了如何通过具体的电路配置实现功能完备的三值逻辑门。通过图示的电路和真值表,能够看到不同输入条件下T-NAND和T-NOR逻辑门的表现,最后的性能评估展示了该电路配置在实际操作中的效果。

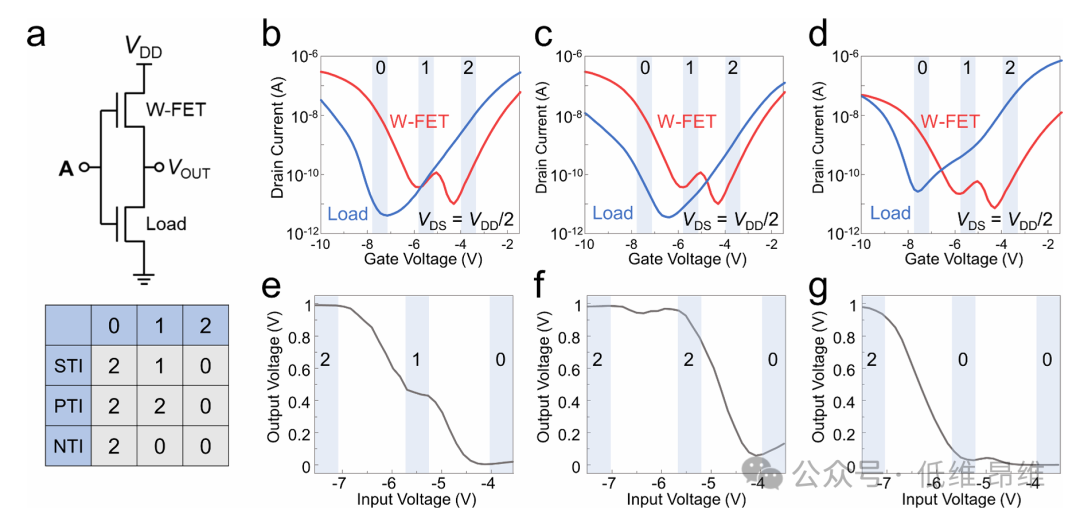

图5

:(a) 单输入三值反相器(STI、PTI和NTI)的电路配置及其相应的真值表。(b

−

d) 在VDS = VDD / 2下,用于STI(b)、PTI(c)和NTI(d)的W-FET和负载的转移曲线。突出显示的栅极电压范围表示输入0、1和2。(e

−

g) STI(e)、PTI(f)和NTI(g)的输入

−

输出电压特性,展示了正确的输出信号。突出显示的输入电压范围对应于(b

−

d)中的输入0、1和2。

结论与展望

总体而言,此研究展示了在二维范德华WSe2材料上制造的同质结NDT器件不仅具有更简单的结构和制造过程,消除了当前NDT技术中普遍存在的复杂异质结结构,而且还提供了之前无法实现的先进三值计算功能,能够执行任何三值逻辑操作。本研究突出了NDT器件作为三值计算强大平台的潜力。

文献信息

Electron-Beam-Induced Negative Differential Transconductance Homojunction Device Based on van der Waals Materials for Functionally Complete Ternary Computing

(ACS Nano,DOI:10.1021/acsnano.4c11169)

文献链接:https://doi.org/10.1021/acsnano.4c11169

上

海

昂

维

科

技

有

限

公

司

现

提

供

二

维

材

料

单

晶

和

薄

膜

等

耗

材

,

器

件

和

光

刻

掩

膜

版

定

制

等

微

纳

加

工

服

务

,以及各种测试分析,

欢

迎

各

位

老

师

和

同

学

咨

询

,

竭

诚

做

好

每

一

份

服

务

。