现在堆叠芯片的方法得到了更多的关注,但支持堆叠芯片的设计流程似乎还不是很成熟。

先进封装技术被看作是摩尔定律的一种替代品,或者是一种增强它的方法。但是,在证明这些器件能够以足够的产量生产与先进封装对设计和验证流程的要求之间还存在着很大的差距。

并非所有的先级封装都对工具和方法有相同的要求。2.5D封装与单片3D集成电路的封装要求大不相同。其他还有小晶片、各种类型的扇出和扇入、系统级封装,以及层叠封装(PoP)和引线键合的方法。根据封装类型的不同,可能需要混合使用印刷电路板和集成电路设计技术和工具。但无论使用哪种封装,正规的验证方法必不可缺。

那么,我们来谈谈该行业应该在哪里做调整,或添加必要的工具及流程,以使该技术可用于更广泛的行业呢?

市场领导者的特征总是第一个转向最新的节点,因为这为他们提供了保持竞争优势所需的扩展性、能力和性能优势。“对于大多数人来说,整体式规模扩张即将结束,”西门子Mentor产品营销经理Keith Felton表示。“7纳米是非常昂贵的,必须生产数百万个晶圆才能覆盖NRE费用。当设计一个大的芯片时,最好的方法是把设计分成更小的模块,在那里你可以为芯片的那部分使用适当的节点或技术,然后把它集成到硅中介层上。你可在短时间内得到便宜得多的东西,这样可以更快地上市。如果你想做一个更新的产品,你只需更换一两个芯片就可以得到,而不需要重新设计一个全新的SOC。”

虽然这其中有一些可能是对未来的预测,但这正是推动该行业发展的主要因素。

“我们现在有一些选择,虽然目前成本还相当高,但有很多优势,”Cadence IC封装产品总监John Park说。“在过去的几年里,我们已经从一个小的印刷电路板过渡到看起来很像一个大规模的集成电路。”

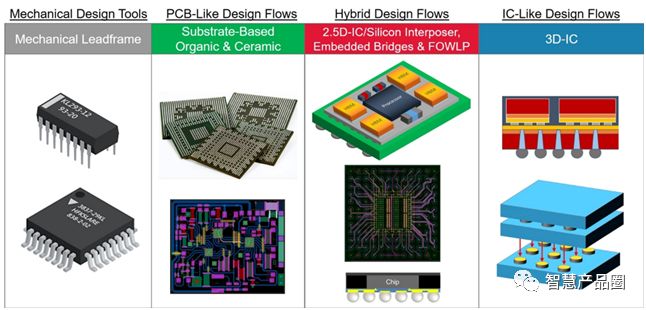

Park列举了行业从引线框架到球网格阵列(BGA),再到2.5D和3D技术的发展道路(图1)。

▲ 封装技术的发展和开发流程 (来源:Cadence)

使用2.5D,您可以从板上移动存储,并使用硅中介层将其集成到处理器旁边,这可以通过缩短距离和扩大数据管道来减少延迟。“您使用什么工具来实现中介层?“Park问。“布线和布线后都使用什么工具?怎么tape out(交付制造)?它需要用一种集成电路的格式交付制造。从历史上看,封装是以印刷电路板格式(如Gerber或IPC2581)tape out的。

这将对工具产生很大的影响。“你需要一种类似PCB(印刷电路板)的技术来布线,因为在交互式和手动布线方面,它们比传统的IC工具要先进一些,后者往往是批处理应用程序,”他指出。“但我也需要一些集成电路技术。我需要创建光罩层和GDS,因为它们将使用IC设计工艺来制造。一旦我们进入三维集成电路,它从设计规划到验证测试确认(signoff),包括时间分析,这是一个纯粹的集成电路工艺。另外,您还需要多芯片的LVS检查。封装设计师从一个电路板设计师变成了一个芯片设计师。它还扩展到生态系统中,每一个新的封装变种都需要一个流程参照和相关的PDK(Process Design Kit)。”

这不仅仅是变换工具,风格随着工具的变化也在变化。“我想知道在验证组件的封装设计时,有多少刚性或形式性,”Mentor的技术营销工程师JohnFerguson说。“过去有一个粗略的设计规则手册,如果你遵循它的规则,你就可以制造出来。用户可以通过肉眼观察来了解这一点,大多数人都不太关注。现在我们谈论的是几十万、或数百万个管脚,想通过观察的方法来检查它们是万万不可能的。”

美国国防部高级研究计划局(DARPA)推出了一项名为“CHIPS”的计划,这项计划推出了一个小晶片(chipelets)的概念。“过去,所有IP都在同一个节点上,”Park解释说。“现在,您将以一种与节点无关的方式将其分解并重新构建。SERDES可以是28纳米,内存可以是32纳米,视频芯片可以是7纳米,等等,我具有这种灵活性。但比这些要复杂多的是,因为芯片是物理上实现的第三方IP版本。”在流程方面需要在物理和协议级别上进行一些额外的工作。

抽象建模和模型

整个封装需要作为一个单芯片来处理吗?

“我们现在已经面临一个挑战,要对1亿个门电路的设计进行分析和验证。”Synopsys的三维IC布局和验证应用工程师Frank Malloy说。“现在你在上面再堆1亿个门电路,如果你试图把它当作一个巨大的设计,你的存储器使用和运行时间将失控。我们需要用抽象建模的方式来概括某些设计,并减少对存储存和运行时间的影响。”

但还有一些其他关键信息,必须在各部分之间共享。“在当今复杂的设计中,IR压降分析至关重要。”Malloy伊说。“现在,当一个大的芯片上有另一个芯片时,你必须计算出它的IR压降,它必须通过下芯片将电源和接地通过封装输送到上芯片。上芯片的IR压降将会受到下芯片IR压降的影响,因此我们必须进行多芯片IR压降分析。”

在一个设计环境下将这些部分组合在一起是具有挑战性的,或者说也是降低复杂性的一种方式。

“对于试图将多个芯片集成到一个系统中并试图处理此类相互影响的任何人来说,基于模型的接口都是一个很好的解决方案,”Ansys模拟和混合信号解决方案高级产品经理Karthik Srinivasan说。“IR压降可以以提取的方式进行,但是对于组装系统并拥有一个真正的3D IC的人来说,其中一个芯片与凸块接口,另一个芯片通过凸块连接,他们需要知道芯片上的负载,以便进行真正的IR压降分析,您需要一个并行仿真处理。”

如今,这些抽象的概念并不标准。“今天确实存在一些必要的抽象概念,但每个供应商都有自己的特点和做事方式,”Ferguson指出。“在代工厂和用户之间,随着时间的推移,它们将结合在一起,我们将实行相同的设计惯例。”

最终,标准机构将参与其中。“有一些标准机构,如SI2,正试图对其中一些抽象概念提出一个无IP的定义,”Felton解释说。“然而,现在有很多格式,它们可能不是很理想的,但从LEF/DEF文件、GDS文件、逗号分隔值电子表格、AIF文件到BGA.txt文件,无所不包。你必须在早期要仔细,不要太拘束。这可能会迫使用户进入特定的使用模型。我们看到客户在处理同一问题的方式上非常多样化,他们使用不同形式的数据。他们想要的是一个尽可能开放的解决方案,这样他们就不会被迫进入限制性的数据流程。”

接口

在小晶片(chiplets)概念成为现实之前,需要制定标准接口。“高带宽内存(HBM)是一个早期的例子,”Park说。“这有点简单,因为它只是一个针对特定应用的内存接口。小晶片接口必须更通用。”

DARPA的CHIPS项目正在解决这个问题。他们选择了先进的接口总线(AIB)作为一个物理层接口,由英特尔开发,用于在其嵌入式多芯片互连桥(EMIB)中进行芯片到芯片的连接。英特尔通过DARPA计划使AIB成为可用的、免版税的总线标准。其他公司正在开发运行在此接口之上的轻量级协议。

但可能需要多个专用接口。“HBM是一个高度并行化的接口,在这里你可以移动大量的数据,而不需要借助高速的IOs,”Felton解释说。“它给你的吞吐量几乎没有功耗,因此减少了热问题。有PAM4,外面有很多协议接口支持。根据芯片类型及其功能,小晶片将根据所需性能支持一个或多个标准接口。”

工具与流程

今天,封装必须进行设计,并且可能需要进行分段设计。布线可能涉及到多个芯片。并且设计分析必须考虑到封装中的所有东西以及更多内容。